- Products

- Automotive

- Avionics

COTS Module

- Zynq RFSoC ADC DAC PCIe Card

- Agilex 7 SmartNIC Card

- ZU7/ZU5/ZU4 PCIe SmartNIC Card

- ZU19/17/11 PCIe SmartNIC Card

- Kintex-7 PCIe Card

- PCIe Switch Module

- PCIe to SD 3.0 M.2 Module

- Zynq ZU7/ZU5/ZU4 3U-VPX

- Virtex UltraScale+ 3U VPX

- Kintex UltraScale+ 3U VPX

- Zynq ZU19/17/11 3U VPX

- Kintex-7 3U VPX Card

- PCIe Gen3 x8 FMC Module

- Quad QSFP28 FMC+ Module

- PCIe Gen4 x16 FMC+ Module

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- FMC Add-On Cards

- FPGA IP

- ODM Solutions

- Custom Design

- Resources

- Company

Get a Quote

Please fill in the form and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Get in Touch

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Thank you for subscribing to our newsletter!

Documents

Evaluation Platforms

Accessories

Additional Details

Documents

Evaluation Platforms

Accessories

Additional Details

SATA Host Controller

SATA Host Controller

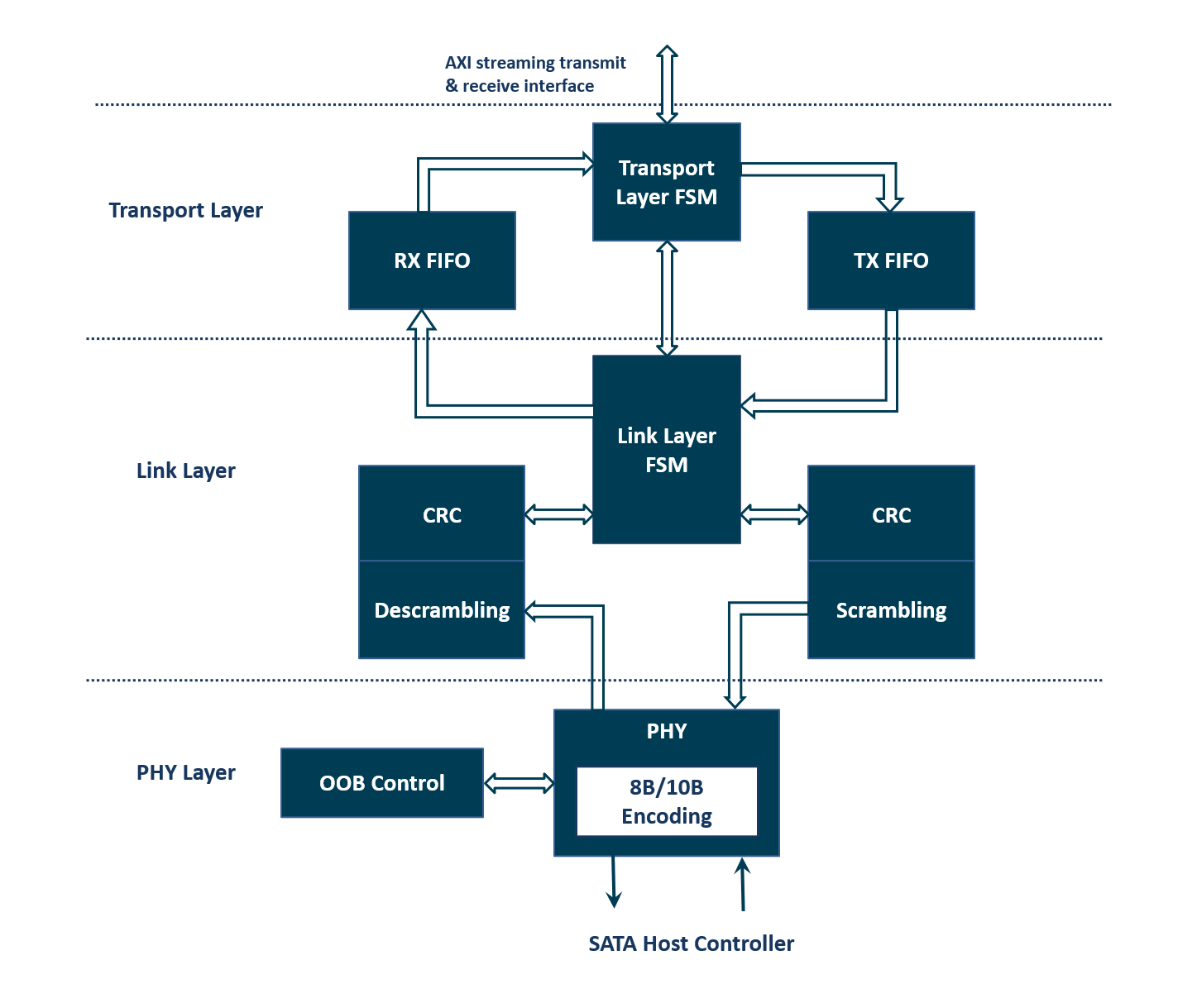

The SATA Host Core is available for integration into host FPGA designs to provide an industry-compliant SATA 1.5-Gbps, SATA 3.0-Gbps, and SATA 6.0-Gbps interface. Serial ATA (SATA) are computer bus standards that have the primary function of transferring data (directly or otherwise) between the FPGA and mass storage devices such as a hard disk. SATA host controller along with AHCI controller enables the software to communicate with the SATA drives which are best suited for SOC devices.

SPECIFICATION

- Phy layer consists of Transceiver available in the FPGA which convert the parallel data to serial

- Phy layer supports clock recovery from serial data, 8B/10B encoding and decoding, Byte ordering and word alignment and OOB signalling

- Link layer supports the frame transmission and reception

- Link layer supports frame formation by adding the envelope and frame decomposition by removing envelope from received data

- Link layer supports CRC generation and calculation as well as scrambling and descrambling

- Link layer supports host and device flow control

Link layer supports primitives such as ALIGN, DMAT, EOF, HOLD, HOLDA, R_ERR, R_IP, R_OK, R_RDY, SOF, SYNC, WTRM, X_RDY

Transport layer supports 32 bit AXI stream interface for Tx and RX towards user interface

Transport layer supports formatting of the FISes and control information based on FIS type

Transport layer reports frame transmission and reception as well as error status

Transport layer supports FISes such as Register FIS, DMA Activate FIS, DMA Setup FIS, Data FIS, PIO Setup FIS, Set Device Bits FIS

HIGHLIGHTS

- AHCI controller along with SATA host controller best suits for SOC devices and SATA controller without AHCI layer can be used with Non-SOC FPGA devices

- Controller provides simple AXI streaming TX and RX interface for the communication with the Application layer.

- Supports Native Command Queuing and most of the primitives and FIS types defined in SATA specification.

EVALUATION PLATFORMS

ZCU102 Dev Kit

iWave SATA host controller IP is tested in Zynq MPOSC based devices from AMD/Xilinx using ZCU102 dev kit and iWave’s FMC daughter card. This daughter card is equipped with the SATA connector to test the IP functionality.

KC705 Dev Kit

iWave SATA host controller IP is tested in 7 series FPGA devices from AMD/Xilinx using Kintex 7 based KC705 dev kit and iWave’s FMC daughter card. This daughter card is equipped with the SATA connector to test the IP functionality.

Stratix 10 SX Dev Kit

iWave SATA host controller IP is tested in Stratix 10 based devices from Intel using Stratix 10 SX dev kit and iWave’s FMC daughter card. This daughter card is equipped with the SATA connector to test the IP functionality.

Arria 10 GX Dev Kit

iWave SATA host controller IP is tested in Arria 10 based devices from Intel using A10 GX dev kit and iWave’s FMC daughter card. This daughter card is equipped with the SATA connector to test the IP functionality.

RELATED VIDEOS

Related products

Download

Please fill in the form below to download the document.

Thanks for filling in the download form.

Request Document

Please fill in the form below and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

iWave is an embedded systems engineering and solutions company, designing solutions for the Industrial, Medical, Automotive and Avionics vertical markets, and building on our core competency of embedded expertise since 1999. Read More…

Newsletter

Copyright © 2022 iWave Systems Technologies Pvt. Ltd.