- Products

- Automotive

- Avionics

PCIe Cards

FMC Cards

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x16 FMC+ Module

- PCIe Gen4 x16 FMC+ Module

- PCIe Gen3 x8 FMC Module

- Quad QSFP28 FMC+ Module

- PCIe Gen3 x8 FMC Module

- Quad QSFP28 FMC+ Module

- FMC Add-On Cards

- FMC Add-On Cards

COTS Module

- Agilex 7 SmartNIC Card

- Zynq RFSoC ADC DAC PCIe Card

- ZU7/ZU5/ZU4 PCIe SmartNIC Card

- ZU7/ZU5/ZU4 PCIe SmartNIC Card

- ZU19/17/11 PCIe SmartNIC Card

- ZU19/17/11 PCIe SmartNIC Card

- PCIe Switch Module

- PCIe to SD 3.0 M.2 Module

- PCIe Switch Module

- PCIe to SD 3.0 M.2 Module

- Kintex-7 PCIe Card

- Kintex-7 PCIe Card

- Zynq ZU7/ZU5/ZU4 3U-VPX

- Zynq ZU7/ZU5/ZU4 3U-VPX

- Virtex UltraScale+ 3U VPX

- Virtex UltraScale+ 3U VPX

- Kintex UltraScale+ 3U VPX

- Kintex UltraScale+ 3U VPX

- RFSoC 3U VPX

- RFSoC 3U VPX

- Agilex 9 3U VPX

- Zynq ZU19/17/11 3U VPX

- Zynq ZU19/17/11 3U VPX

- Kintex-7 3U VPX Card

- Kintex-7 3U VPX Card

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x16 FMC+ Module

- PCIe Gen4 x16 FMC+ Module

- PCIe Gen3 x8 FMC Module

- Quad QSFP28 FMC+ Module

- PCIe Gen3 x8 FMC Module

- Quad QSFP28 FMC+ Module

- FMC Add-On Cards

- FMC Add-On Cards

- IP Cores

- ODM Solutions

- Custom Design

- Company

Get a Quote

Please fill in the form and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Get in Touch

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Thank you for subscribing to our newsletter!

Documents

Evaluation Platforms

Accessories

Additional Details

Documents

Evaluation Platforms

Accessories

Additional Details

SD / SDIO Host Controller 3.0

SD / SDIO Host Controller 3.0

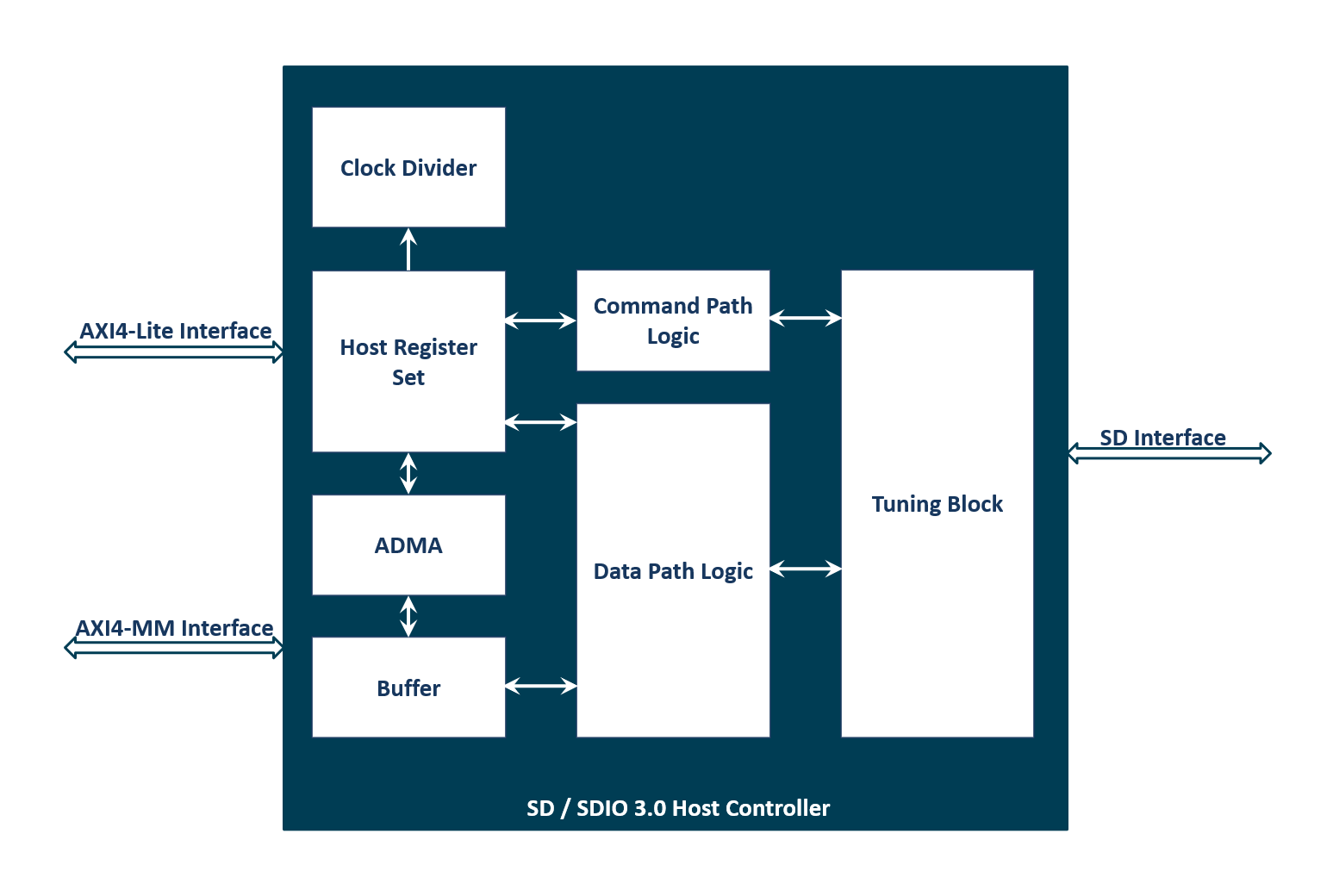

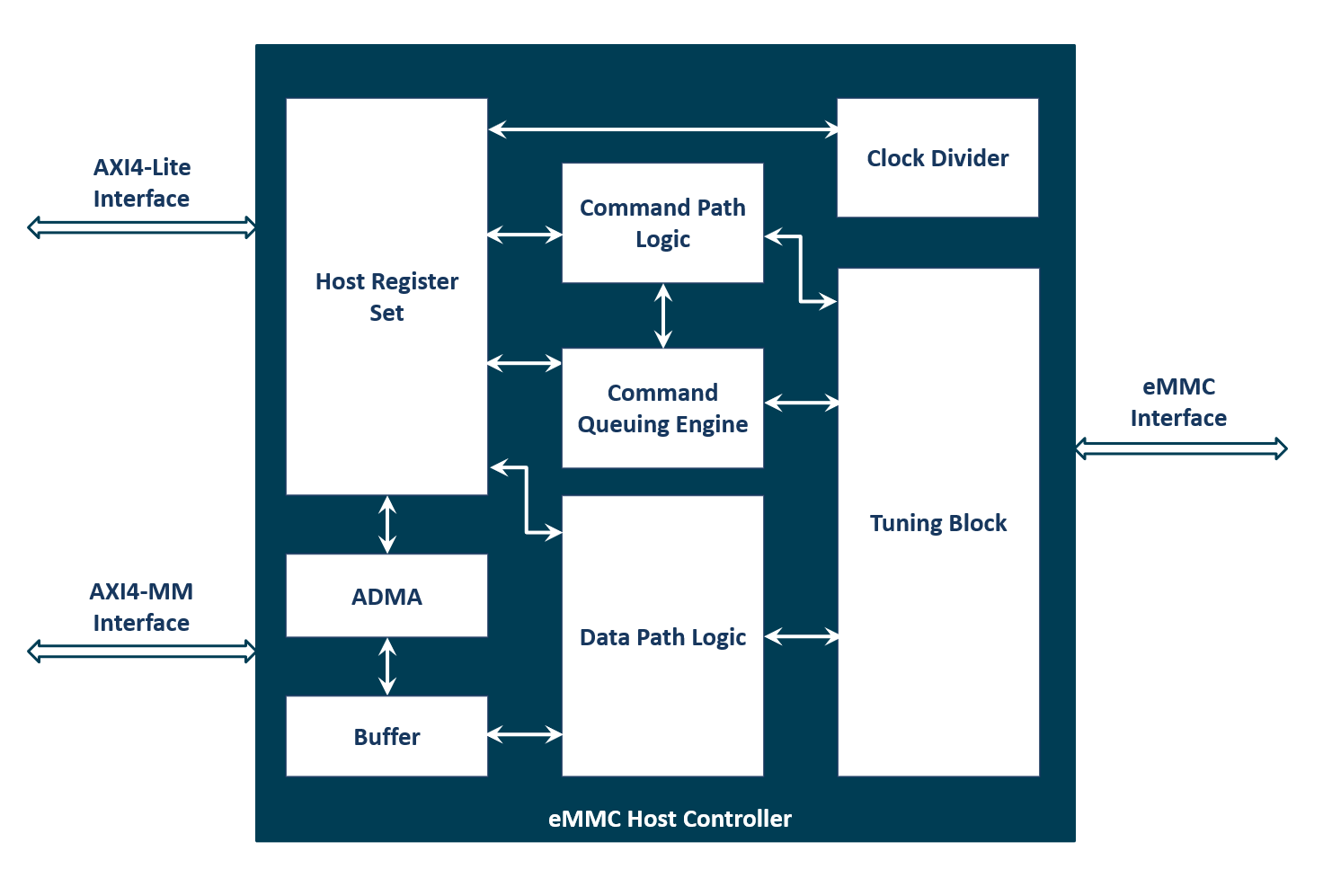

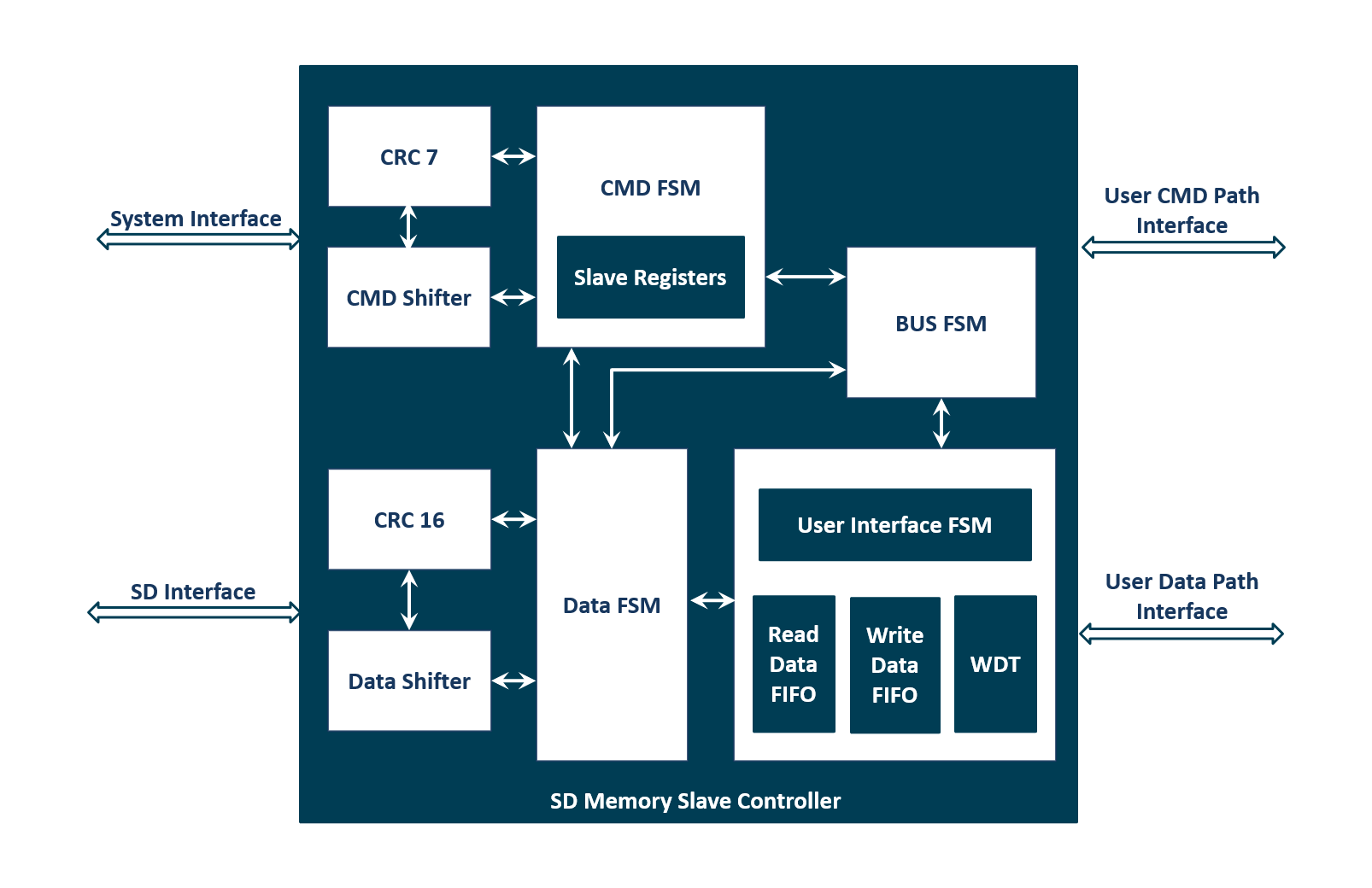

iW-SD/SDIO 3.0 Host controller is compatible with the SD Physical Layer specification V3.0. The core supports AXI4-Lite interface for the control and status register access and AXI4-MM interface for data transfer through ADMA2 mode. The Host interface is compatible with the standard register set for the host controller as per SD host controller specification Version 3.0.

SPECIFICATION

- Compliant with SD Host Controller Standard Specification Version 3.0

- Compliant with SD Physical Layer Specification Version 3.0

- Supports 1-bit,4-bit SD modes

- Supports SD Card Detection input pin

- Supports SD Card Write Protection input pin

- Supports programmable clock frequency generation to the SD card

- Supports Interrupt and ADMA2 transfer mode of operation

- Individual 2Kbyte data buffer for read and write

- Cyclic Redundancy Check (CRC) for command and data

- Supports timeout monitoring for response, data, CRC token & busy

- Supports a maximum block length of 2Kbyte

- Supports both single block and multi block data transfer

- Supports 32-bit AXI4 memory mapped interface towards host processor

- Supports 32-bit AXI4 lite interface towards SD host Controller

- **Support Default speed and High Speed including SDR12, SDR25, DDR50, SDR50 andSDR104 modes

HIGHLIGHTS

- Supports following UHS –I modes of operations:

- SDR12 – SDR up to 25MHz 1.8V signaling

- SDR25 – SDR up to 50MHz 1.8V signaling

- SDR50 – SDR up to 100MHz 1.8V signaling

- **SDR104 – SDR up to 208MHz 1.8V signaling

- Supports programmable clock frequency generation

- Supports standard register set for the host controller

- Core offers UHS-I mode of operation

- Software support includes the standard SD driver for Linux, u-boot and simplified baremetal SD driver

- Supports multiple file systems like FAT32 and ext4

- Supports the MBR and GPT partitions

** IP Supports SDR50 and SDR104 mode. Please contact us to check the SDR50 and SDR104 mode support in target device

EVALUATION PLATFORMS

ZCU102 Dev Kit

SD3.0 host controller IP is tested in Zynq MPOSC based devices from AMD/Xilinx using ZCU102 dev kit and iWave’s FMC daughter card. This daughter card is equipped with the necessary SD3.0 level translator IC to enable SD3.0 functionality.

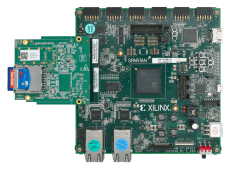

KCU105 Dev Kit

SD3.0 host controller IP is tested in Ultrascale FPGA devices from AMD/Xilinx using Kintex Ultrascale based KCU105 dev kit and iWave’s FMC daughter card. This daughter card is equipped with the necessary SD3.0 level translator IC to enable SD3.0 functionality.

ZED Board

SD3.0 host controller IP is tested in Zynq 7000 based devices from AMD/Xilinx using ZED Board and iWave’s FMC daughter card. This daughter card is equipped with the necessary SD3.0 level translator IC to enable SD3.0 functionality.

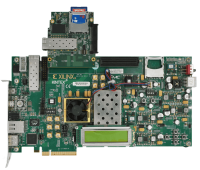

KC705 Dev Kit

SD3.0 host controller IP is tested in 7 series FPGA devices from AMD/Xilinx using Kintex 7 based KC705 dev kit and iWave’s FMC daughter card. This daughter card is equipped with the necessary SD3.0 level translator IC to enable SD3.0 functionality.

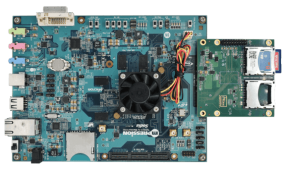

SP701 Dev Kit

SD3.0 host controller IP is tested in 7 series FPGA devices from AMD/Xilinx using Spartan7 based SP701 dev kit and iWave’s FMC daughter card. This daughter card is equipped with the necessary SD3.0 level translator IC to enable SD3.0 functionality.

Sodia Dev Kit

SD3.0 host controller IP is tested in Intel CycloneV FPGA devices using Sodia dev kit and iWave’s FMC daughter card. This daughter card is equipped with the necessary SD3.0 level translator IC to enable SD3.0 functionality.

RELATED VIDEOS

Related products

Download

Please fill in the form below to download the document.

Thanks for filling in the download form.

Request Document

Please fill in the form below and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

iWave is an embedded systems engineering and solutions company, designing solutions for the Industrial, Medical, Automotive and Avionics vertical markets, and building on our core competency of embedded expertise since 1999. Read More…

Newsletter

Copyright © 2022 iWave Systems Technologies Pvt. Ltd.