- Products

- Automotive

- Avionics

PCIe Cards

FMC Cards

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x16 FMC+ Module

- PCIe Gen4 x16 FMC+ Module

- PCIe Gen3 x8 FMC Module

- Quad QSFP28 FMC+ Module

- PCIe Gen3 x8 FMC Module

- Quad QSFP28 FMC+ Module

- FMC Add-On Cards

- FMC Add-On Cards

COTS Module

- Agilex 7 SmartNIC Card

- Zynq RFSoC ADC DAC PCIe Card

- ZU7/ZU5/ZU4 PCIe SmartNIC Card

- ZU7/ZU5/ZU4 PCIe SmartNIC Card

- ZU19/17/11 PCIe SmartNIC Card

- ZU19/17/11 PCIe SmartNIC Card

- PCIe Switch Module

- PCIe to SD 3.0 M.2 Module

- PCIe Switch Module

- PCIe to SD 3.0 M.2 Module

- Kintex-7 PCIe Card

- Kintex-7 PCIe Card

- Zynq ZU7/ZU5/ZU4 3U-VPX

- Zynq ZU7/ZU5/ZU4 3U-VPX

- Virtex UltraScale+ 3U VPX

- Virtex UltraScale+ 3U VPX

- Kintex UltraScale+ 3U VPX

- Kintex UltraScale+ 3U VPX

- RFSoC 3U VPX

- RFSoC 3U VPX

- Agilex 9 3U VPX

- Zynq ZU19/17/11 3U VPX

- Zynq ZU19/17/11 3U VPX

- Kintex-7 3U VPX Card

- Kintex-7 3U VPX Card

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x16 FMC+ Module

- PCIe Gen4 x16 FMC+ Module

- PCIe Gen3 x8 FMC Module

- Quad QSFP28 FMC+ Module

- PCIe Gen3 x8 FMC Module

- Quad QSFP28 FMC+ Module

- FMC Add-On Cards

- FMC Add-On Cards

- IP Cores

- ODM Solutions

- Custom Design

- Company

Get a Quote

Please fill in the form and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Get in Touch

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Thank you for subscribing to our newsletter!

Documents

Intel Evaluation Kit

Mircochip Evaluation Kit

Documents

Intel Evaluation Kit

Mircochip Evaluation Kit

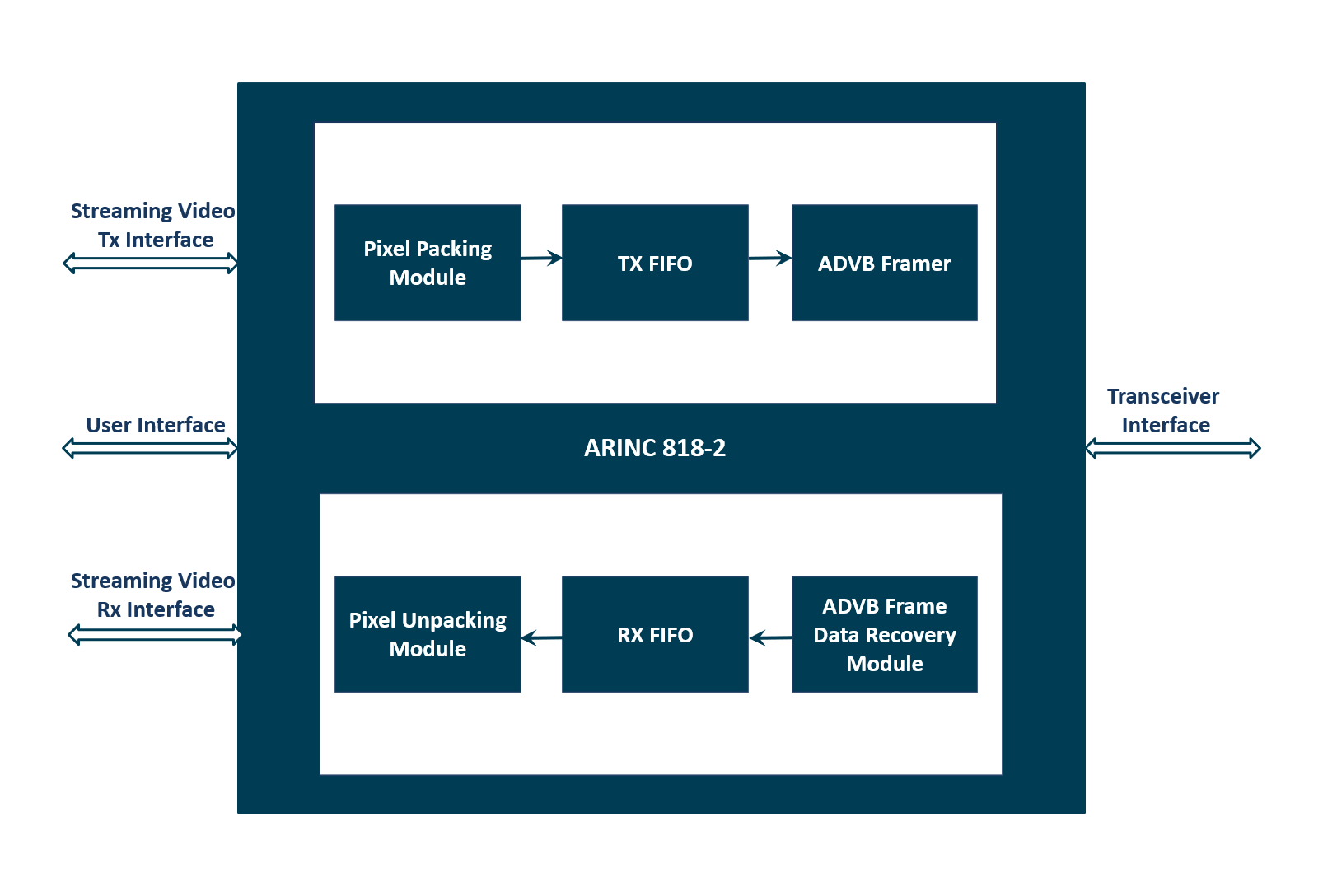

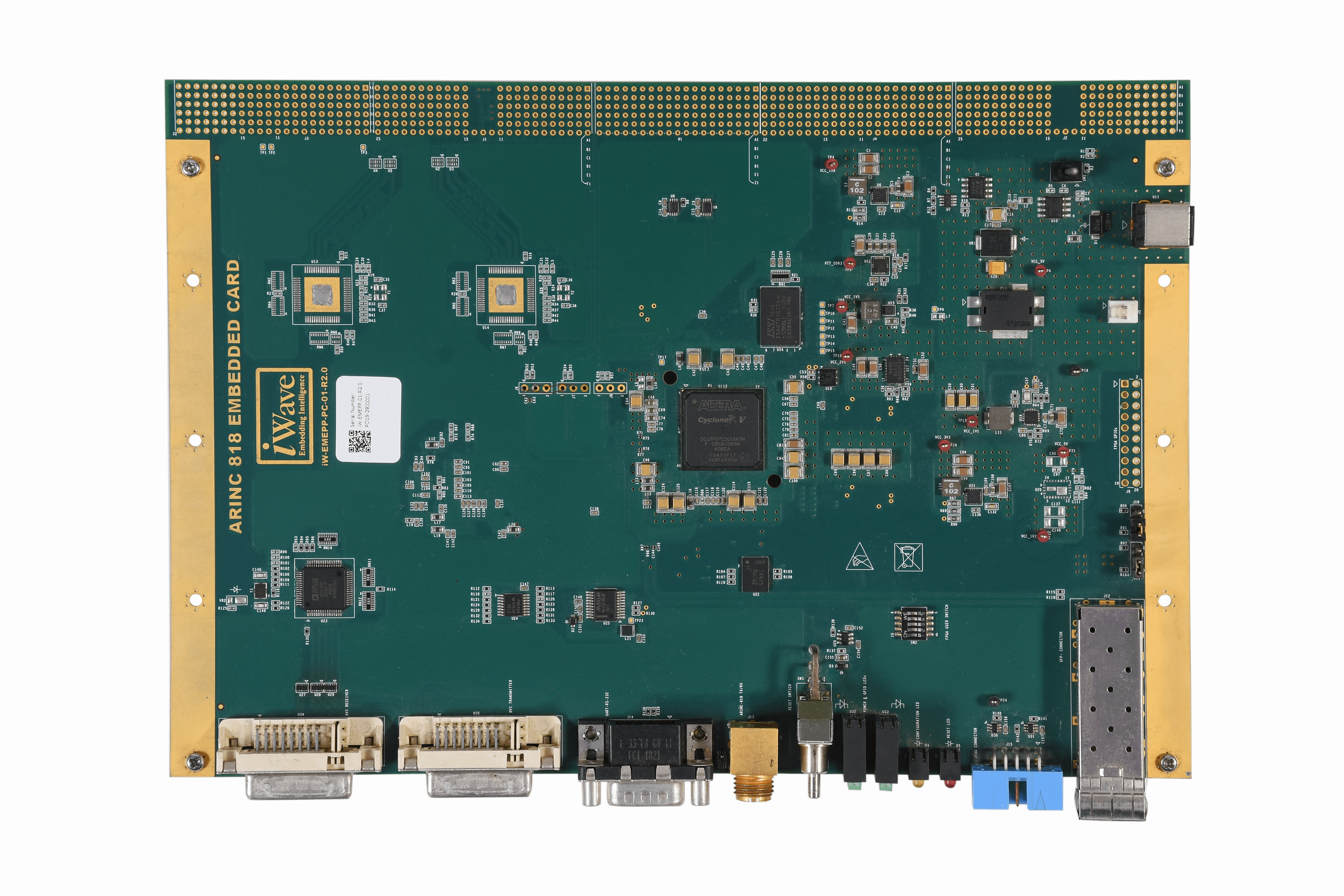

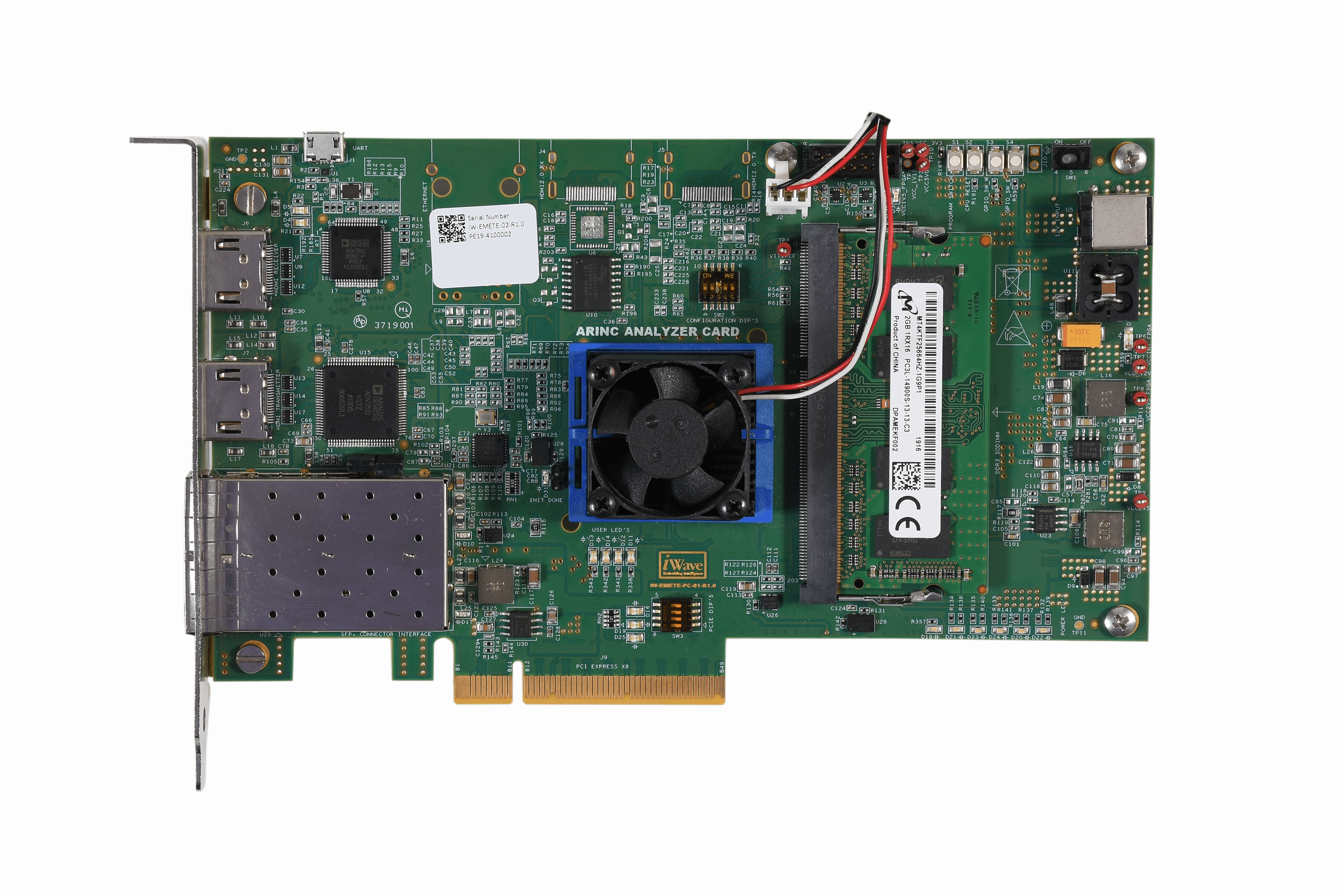

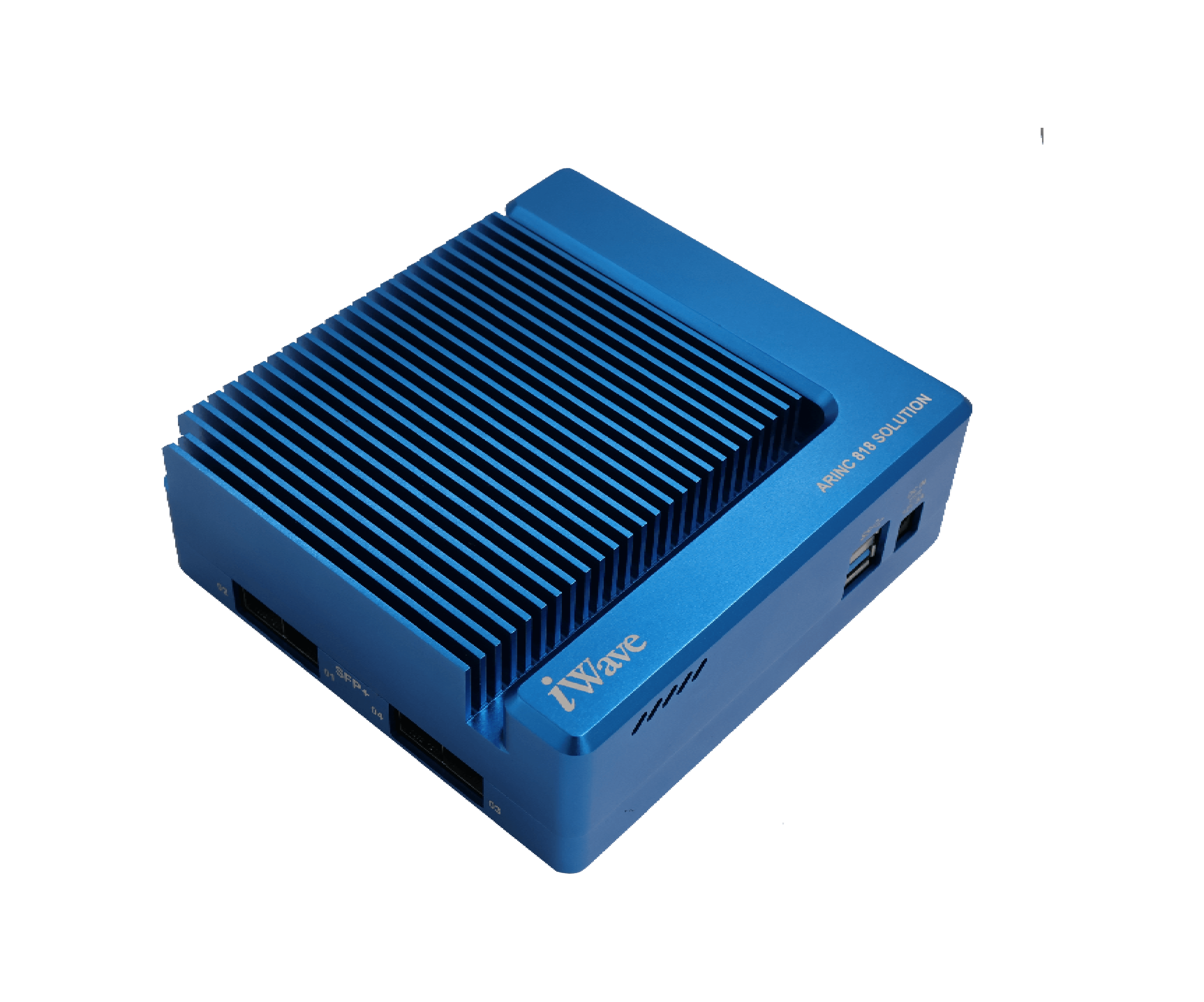

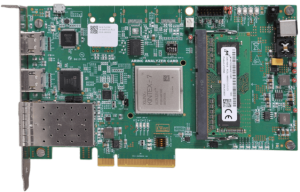

ARINC 818-2 IP Core

ARINC 818-2 IP Core

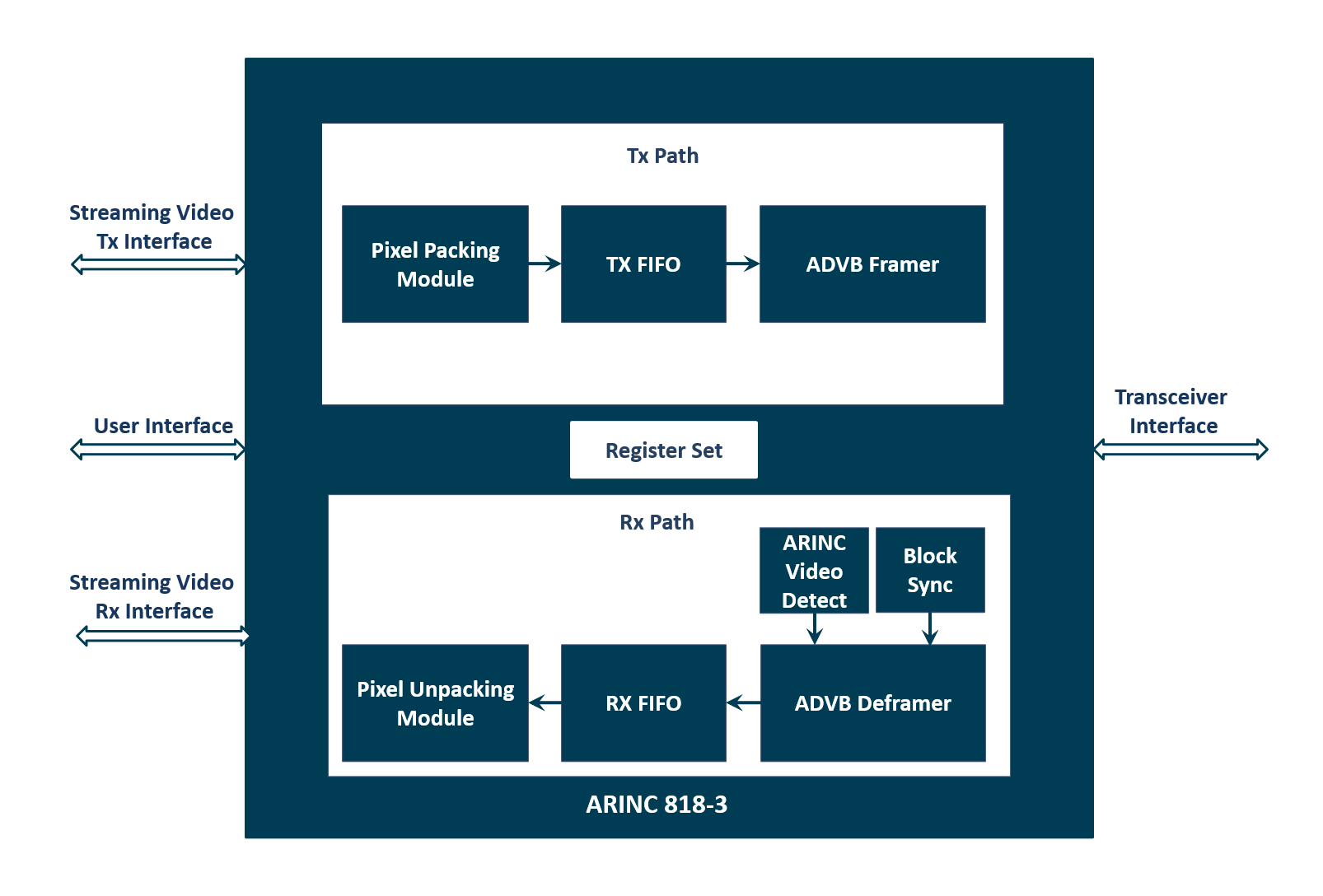

iWave’s ARINC IP core is ARINC 818–2 compliant offering point-to-point, high-speed, low latency video transmission. This IP core can be implemented on any transceiver-based FPGA device. It can be used for both transmit and receive applications. This core supports configurable ADVB video formats and uses a simple streaming interface to interface with video & image processing IP cores supported by FPGA vendors.

SPECIFICATION

- IP Compliant to ARINC 818-2 specification

- Video TX and RX interface: Simple Streaming Interface

- Custom data transmission & reception during the video blanking period

- Transmission Medium

- Optical or

- 75-ohm, 100-ohm or 150-ohm Copper

- Link Rate Supported

- FC 1x, 2x, 3x, 5x, 6x, 8x & 12x

- Video Resolution Supported

- Resolution up to 4K @ 60fps

- Video Type

- Progressive Scan

- Interlaced

- Pixel Format supported

- Monochrome

- RGB

- YcbCr

- RGBA

- Pixel Aspect ratio supported.

- 1:1

- 1:1.2

- 1.2:1

- NTSC (approx 8:9)

- PAL (16:15)

- Frame Rate supported.

- 15fps

- 20fps

- 24

- 24 * 1000 / 1001

- 25 (PAL)

- 30

- 30 * 1000 / 1001 (29.97 NTSC)

- 60

- 50

- 60 * 1000 / 1001 (59.94 NTSC)

- 50 (VESA DMT)

- 60 (VESA DMT)

- 75 (VESA DMT)

- 85 (VESA DMT)

- 50 (VESA CVT)

- 60 (VESA CVT)

- 75 (VESA CVT)

- 85 (VESA CVT)

- Pixel Table Number supported

- 8-bit Components, four components per transmission word

- Pixel Array Order supported

- Left to Right, Top to Bottom

- Line Synchronous Mode supported

- User-configurable parameters as per ICD requirement

- No. Of rows

- No. Of Columns

- Video Format Code

- Pixel Aspect Ratio

- Video Frame rate

- Color Information Code

HIGHLIGHTS

- Quick customization as per customer’s Interface Control Document (ICD) and deliver the same within 3-4 weeks’ timeline.

- Our IP core is not limiting the maximum resolution support and it completely depends on FPGA transceiver speed

RELATED VIDEOS

Related products

Related News

Download

Please fill in the form below to download the document.

Thanks for filling in the download form.

Request Document

Please fill in the form below and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

iWave is an embedded systems engineering and solutions company, designing solutions for the Industrial, Medical, Automotive and Avionics vertical markets, and building on our core competency of embedded expertise since 1999. Read More…

Newsletter

Copyright © 2022 iWave Systems Technologies Pvt. Ltd.