- Products

- Automotive

- Avionics

COTS Module

- Zynq RFSoC ADC DAC PCIe Card

- Agilex 7 SmartNIC Card

- ZU7/ZU5/ZU4 PCIe SmartNIC Card

- ZU19/17/11 PCIe SmartNIC Card

- Kintex-7 PCIe Card

- PCIe Switch Module

- PCIe to SD 3.0 M.2 Module

- Zynq ZU7/ZU5/ZU4 3U-VPX

- Virtex UltraScale+ 3U VPX

- Kintex UltraScale+ 3U VPX

- Zynq ZU19/17/11 3U VPX

- Kintex-7 3U VPX Card

- PCIe Gen3 x8 FMC Module

- Quad QSFP28 FMC+ Module

- PCIe Gen4 x16 FMC+ Module

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- FMC Add-On Cards

- FPGA IP

- ODM Solutions

- Custom Design

- Resources

- Company

Get a Quote

Please fill in the form and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Get in Touch

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Thank you for subscribing to our newsletter!

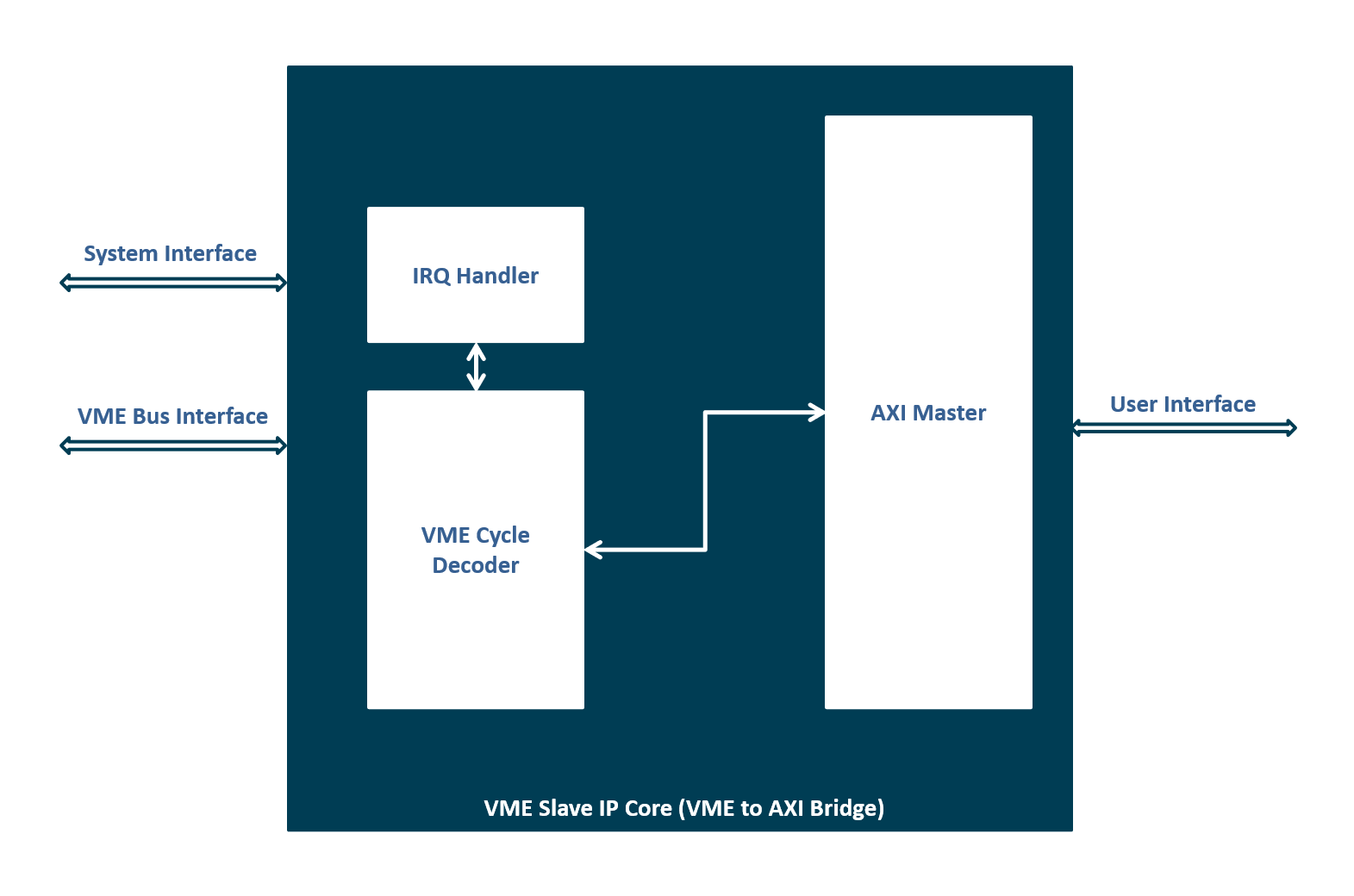

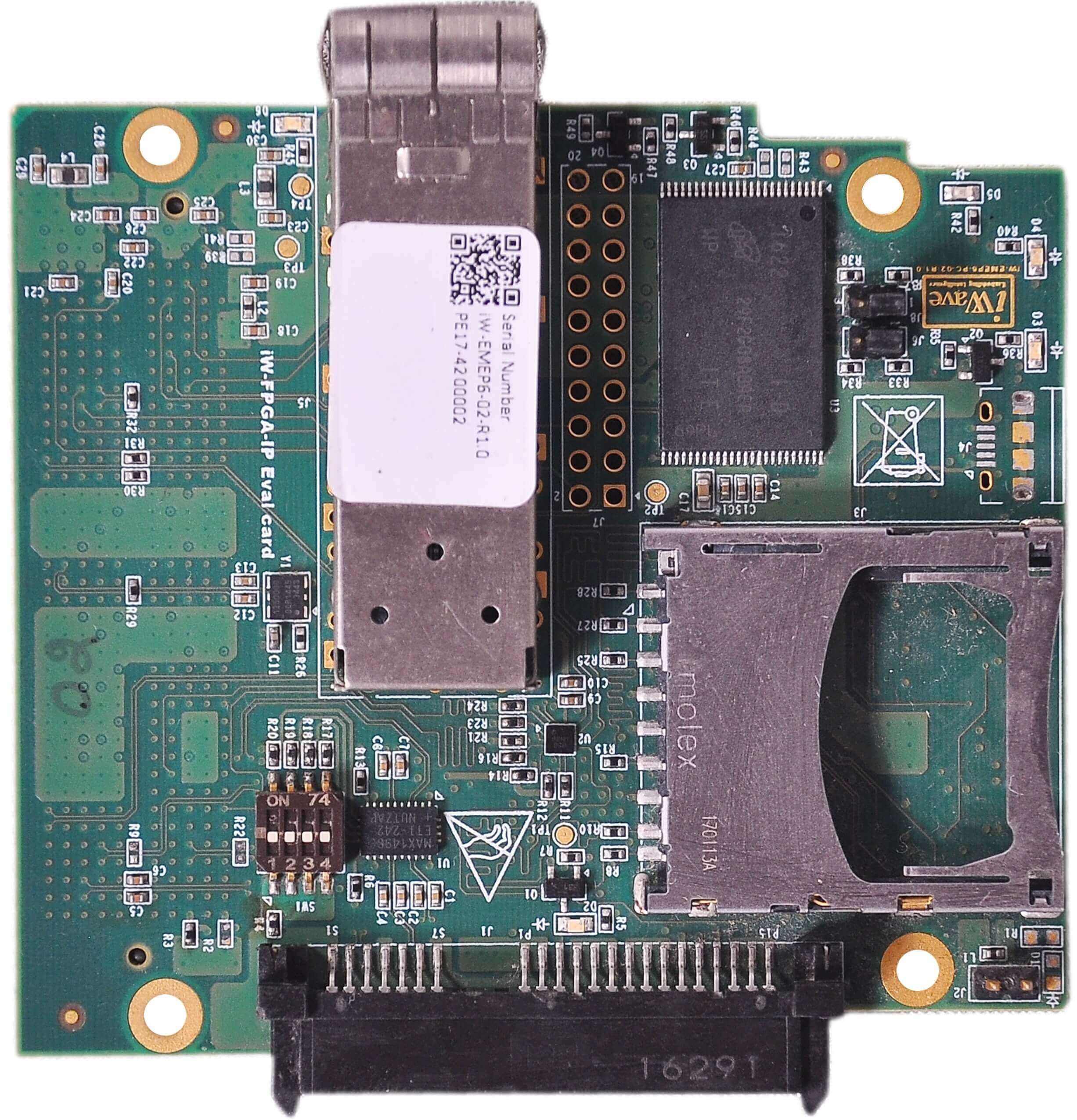

VME Slave IP Core (VME to AXI Bridge)

VME Slave IP Core (VME to AXI Bridge)

The ANSI/VITA 1.0-1994 or VME64 specification establishes a framework for 8-, 16-, and 32-bit parallel bus computer architectures that can implement single and multiprocessor systems. The VMEbus specification defines an interfacing system used to interconnect microprocessors, data storage, and peripheral control devices in a closely coupled hardware configuration.

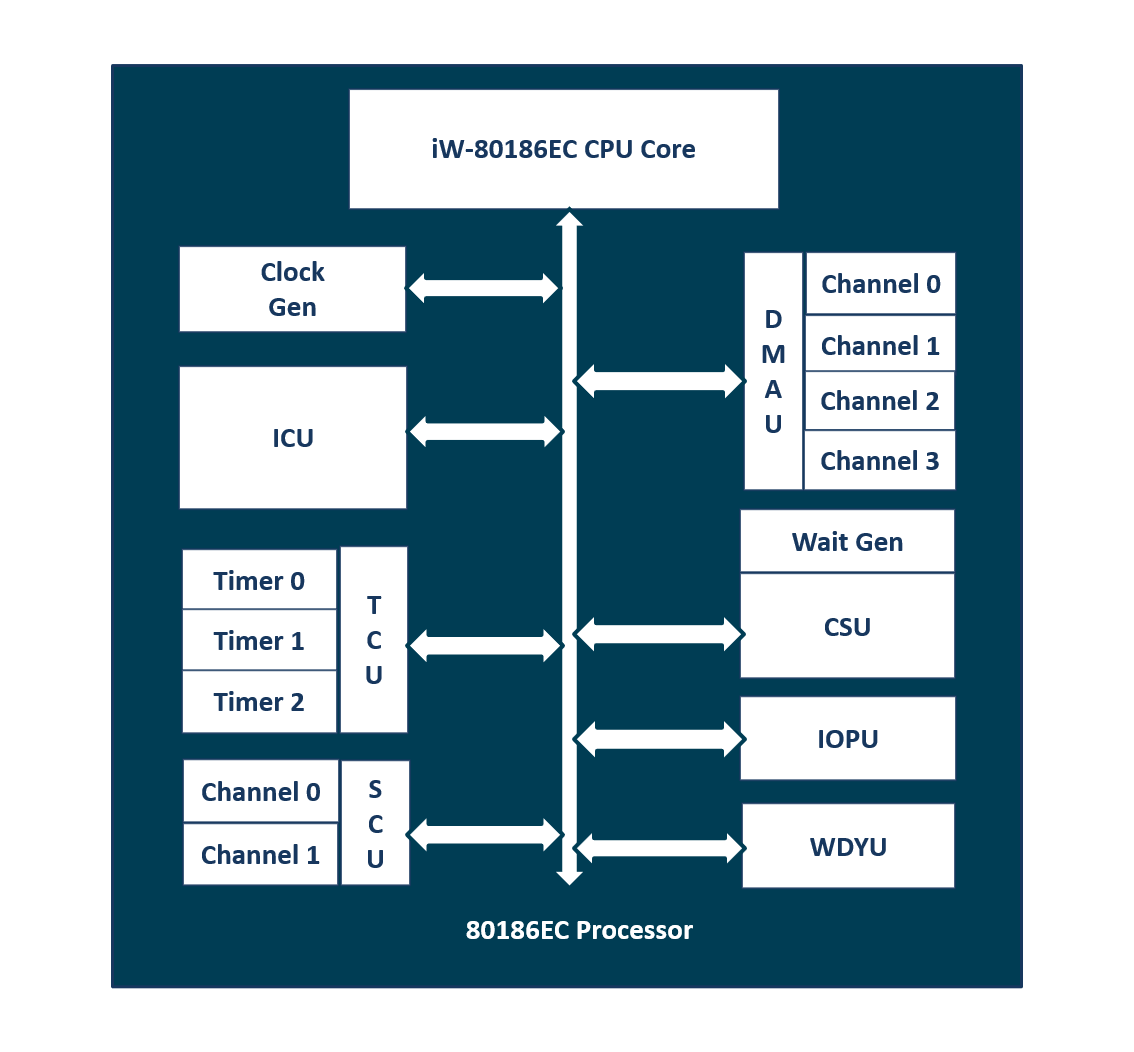

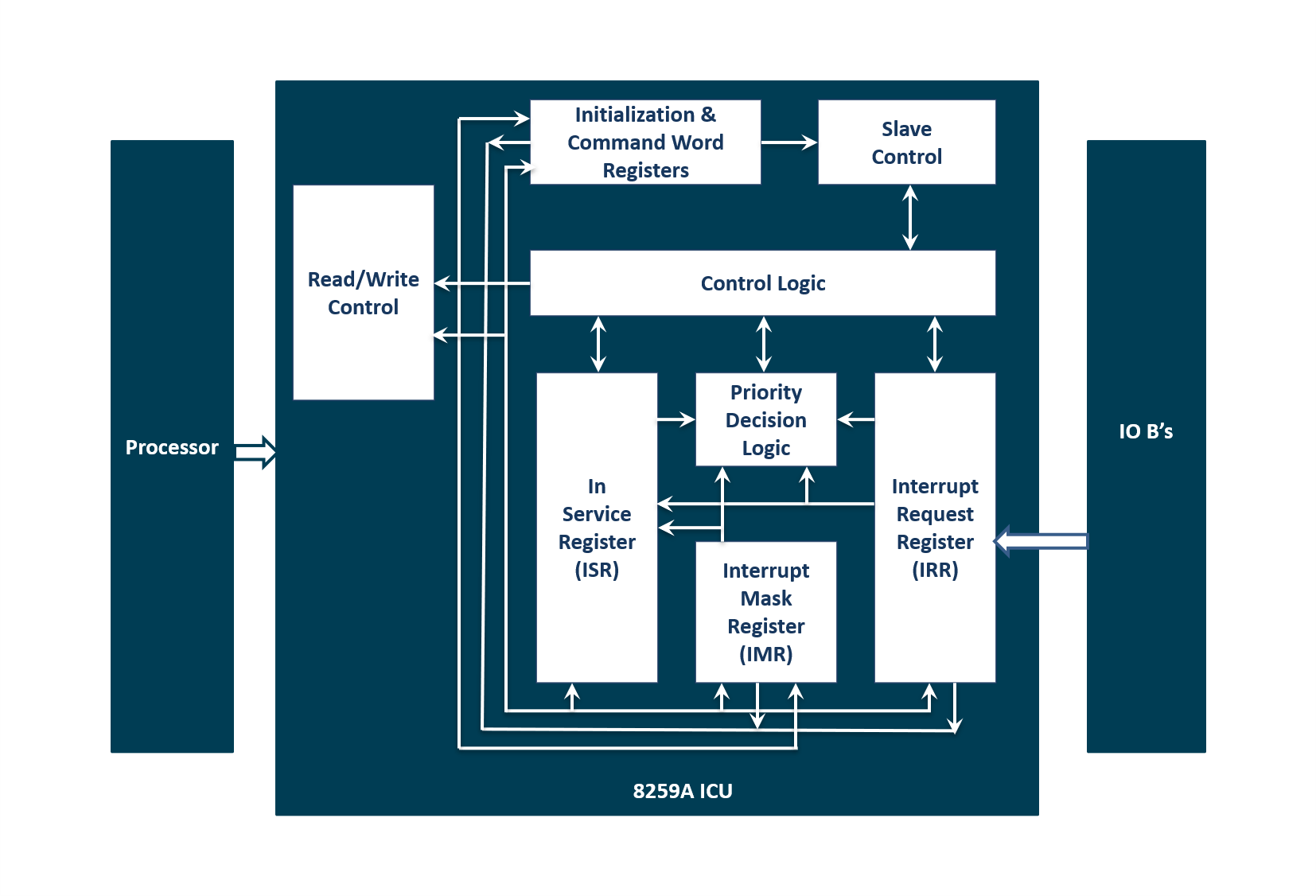

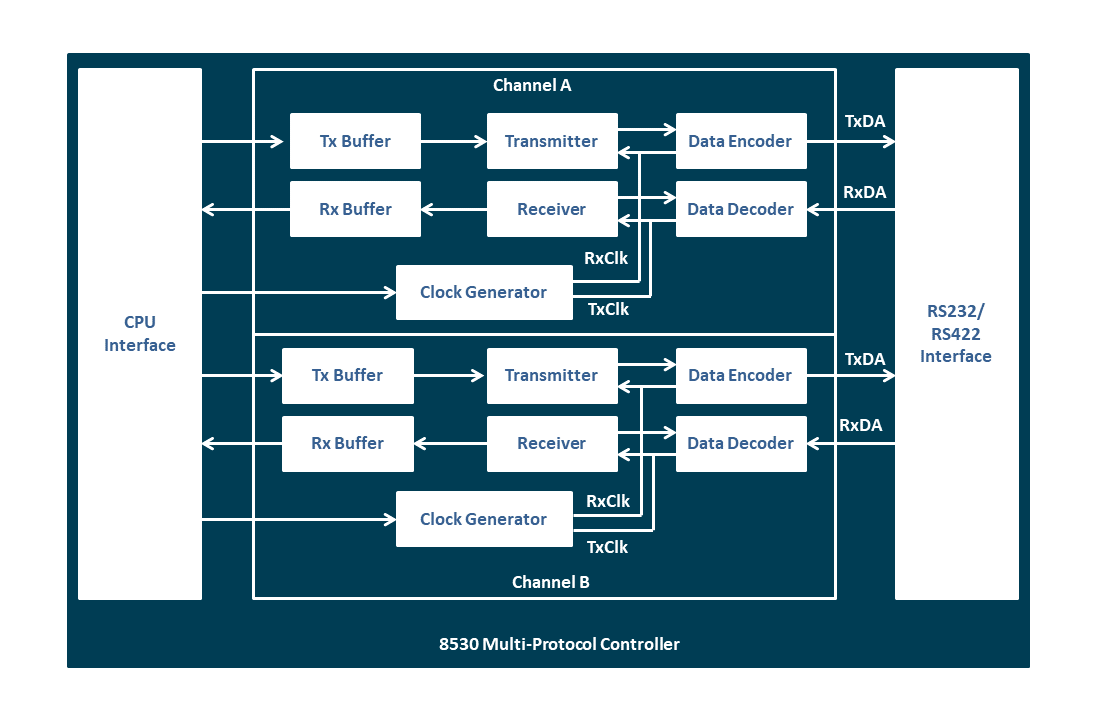

iWave’s IP is compliant to ANSI/VITA1.0-1994 and implements the slave configuration of VMEbus data transfer layer consisting of the Data Transfer Bus and the Priority Interrupt Bus modules. This IP can be considered as a VME to AXI bus bridge and can be implemented in any FPGA having interface to a VME Bus Interface.

SPECIFICATION

- Compliant with ANSI/VITA 1.0-1994 VME64 Bus Standard

- VME to AXI Bus Bridge

- VME bus Module Type

- Slave with Priority Based Interrupts

- Board Address: Hardware Configurable up to 8 bits

- Data Format Supported: 16 bits and 8 bits

- Transfer Modes

- Write & Read

- Block Write & Read

- Address Modes

- A32 Slave: 09, 0B, 0D and 0F (Data and Block Transfer)

- A24 Slave: 39, 3B, 3D and 3F (Data and Block Transfer)

- A16 Slave: 29 and 2D (Data Access, No Block Transfers)

- Block Transfer

- Maximum 256 bytes

- User Interface: AXI-4 Lite

HIGHLIGHTS

- Core is compliant to ANSI/VITA 1.0-1994

- VME Slave IP provides a bus bridge between VME and AXI interfaces

- Supports A32, A16 and A8 addressing modes with D16 data

RELATED VIDEOS

Related products

Download

Please fill in the form below to download the document.

Thanks for filling in the download form.

Request Document

Please fill in the form below and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

iWave is an embedded systems engineering and solutions company, designing solutions for the Industrial, Medical, Automotive and Avionics vertical markets, and building on our core competency of embedded expertise since 1999. Read More…

Newsletter

Copyright © 2022 iWave Systems Technologies Pvt. Ltd.