iWave、最大3.2Gb/秒の比類ない速度を実現するeMMCリビジョン5.1のリリースを発表

JEDECによって定義されたeMMC 5.1仕様は、次のレベルの高速データ転送を可能にし、低ピン数、高帯域幅、マルチブートメカニズムにより、次世代製品への容易な移行と簡素化されたシステム設計を提供します。

iWaveのeMMC 5.1ホストコントローラIPは、最新のeMMC仕様に準拠しています。このIPには、高性能HS400拡張ストローブモード、HS400モード、コマンドキューイングエンジン(CQE)、ソフトウェアオーバーヘッドをコントローラにオフロードすることでデータ転送を高効率化するHS200モードのチューニングなど、まったく新しい機能が含まれています。さらに、PHY層でのエンハンスド・ストロボの利用により、動作のシステム信頼性を向上させます。

eMMC 5.1ホストコントローラIPは、ソフトウェアドライバの上位レベルなしでパワーオンブートをサポートすることにより、システム設計を簡素化します。eMMC 5.1 は、デフォルト速度 (@26Mhz)、高速 (@52 Mhz)、DDR52、1 ビット、4 ビット、8 ビットの eMMC モードなど、以前のバージョンの eMMC と下位互換性があり、最大 4096 バイトのブロック長をサポートします。

メリット

- 前世代および将来世代のeMMC規格と互換性があり、システム統合の迅速化と設計リスクおよびコストの低減を実現

- ゲート数と消費電力を削減した、高度にコンフィギュラブルでスケーラブルなIP

- 最大400MB/秒の比類なきスピードを実現

主な特徴

- eMMC仕様バージョン5.1に準拠

- デフォルト速度(26Mhz)、高速(52Mhz)モード、HS200、HS400、HS400拡張モードをサポート

- コマンド・キューイング・エンジンをサポートし、パフォーマンスを向上

- 1ビット、4ビット、8ビットのeMMCモードをサポート

- eMMCカードへのプログラマブルクロック周波数生成をサポート

- HS200モードのチューニングに対応

- インタラプトおよびADMA2転送動作モードをサポート

- 4Kバイトのデータ・バッファを個別に読み書き可能

- コマンドとデータの巡回冗長検査(CRC)

- レスポンス、データ、CRCトークン、ビジー状態のタイムアウト監視をサポート

- 最大4Kバイトのブロック長をサポート

- シングルブロックとマルチブロックの両方のデータ転送に対応

- 自動CMD12機能をサポート

- データ転送用にホスト・プロセッサ向けの32ビットAXI4メモリマップド・インターフェースをサポート

- レジスタ・アクセス用のホスト・プロセッサ向け32ビットAXI4 liteインターフェースをサポート

IP検証と性能テスト

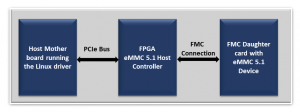

iWaveは、eMMC 5.1ホスト コントローラーの機能と性能を検証するための評価デザインを提供しています。FPGAに実装されたeMMCホストコントローラIPは、PCIeバスを介してホストマザーボードに接続されます。読み取り/書き込み性能を確認するため、eMMC デバイスを搭載した iWave の FMC アドオン カードが FMC スロットを介してボードに接続されています。

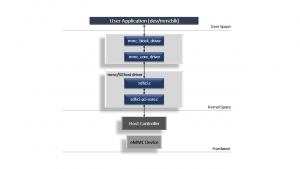

開発環境にはLinux Kernal 5.4.0が含まれる。また、PCIe経由のx86アーキテクチャやARMベースのプラットフォームにも対応しています。

汎用パーティション、ランタイム・モード、バス幅の変更などの豊富な機能をサポートし、デバイスのユーザー領域の拡張を可能にするために、消去、TRIM、サニタイズ、セキュア消去、セキュアTRIM、RPMBなどの機能をサポートしています。カスタムAPIと汎用APIはmmcの一部として提供される。

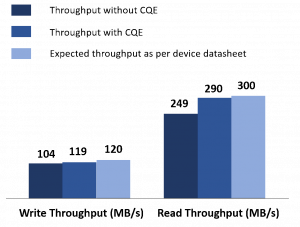

以下に示すパフォーマンス・チャートは、コマンド・キューイング・エンジン(CQE)を使用した場合と使用しなかった場合に観測された書き込み速度と読み込み速度を表している。

iWaveは、IPコアの納品、購入後の不具合保証、電子メール、Skype、または電話による専任の技術サポートにより、ユーザーを保証します。コアは、洗練されたテストベンチ、シミュレーションスクリプト、合成スクリプトなど、実装を成功させるために必要なものがすべて含まれた合成可能なRTLおよびFPGAネットリスト形式で提供されます。IPの成果物には、設計ドキュメント、RTLソースコード、またはデバイス固有のネットリスト、IPデータシート、IP統合マニュアル、期間限定評価バイナリ、eMMCのテスト用カーネルドライバおよびカスタム/汎用APIが含まれます。

IPに関する詳細はこちらをご覧ください。

続きを読む

|  |  |

| 業界準拠のSATA 3.0ホスト・コントローラIP | iWaveがNVMeホスト・コントローラーIPを発表 | SDメモリー・スレーブ・コントローラーを使用したモバイル・セキュリティ・エンジン |