- 製品紹介

- 自動車

- 航空電子工学

FMCカード

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x16 FMC+モジュール

- PCIe Gen4 x16 FMC+モジュール

- PCIe Gen3 x8 FMCモジュール

- クアッド QSFP28 FMC+ モジュール

- PCIe Gen3 x8 FMCモジュール

- クアッド QSFP28 FMC+ モジュール

- FMCアドオンカード

- FMCアドオンカード

COTSモジュール

- Agilex 7 SmartNICカード

- Zynq RFSoC ADC DAC PCIeカード

- ZU7/ZU5/ZU4 PCIe SmartNIC Card

- ZU7/ZU5/ZU4 PCIe SmartNIC Card

- ZU19/17/11 PCIe SmartNICカード

- ZU19/17/11 PCIe SmartNICカード

- PCIe Switch Module

- PCIe to SD 3.0 M.2モジュール

- PCIe Switch Module

- PCIe to SD 3.0 M.2モジュール

- Kintex-7 PCIeカード

- Kintex-7 PCIeカード

- Zynq ZU7/ZU5/ZU4 3U-VPX

- Zynq ZU7/ZU5/ZU4 3U-VPX

- Virtex UltraScale+ 3U VPX

- Virtex UltraScale+ 3U VPX

- Kintex UltraScale+ 3U VPX

- Kintex UltraScale+ 3U VPX

- RFSoC 3U VPX

- RFSoC 3U VPX

- Agilex 9 3U VPX

- Zynq ZU19/17/11 3U VPX

- Zynq ZU19/17/11 3U VPX

- Kintex-7 3U VPXカード

- Kintex-7 3U VPXカード

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x16 FMC+モジュール

- PCIe Gen4 x16 FMC+モジュール

- PCIe Gen3 x8 FMCモジュール

- クアッド QSFP28 FMC+ モジュール

- PCIe Gen3 x8 FMCモジュール

- クアッド QSFP28 FMC+ モジュール

- FMCアドオンカード

- FMCアドオンカード

- IP Cores

- ODMソリューション

- カスタムデザイン

- Company

お見積もり

フォームにご記入ください!

アイウェーブにご連絡いただきありがとうございます。

担当者よりご連絡させていただきます!

お問い合わせ

アイウェーブにご連絡いただきありがとうございます。

担当者よりご連絡させていただきます!

ニュースレターのご購読ありがとうございます!

FPGA設計サービス

FPGA設計の専門知識

FPGA領域で20年以上の経験を持つiWave Systemsは、強力かつ比類のないFPGA設計から展開までの能力を備えています。

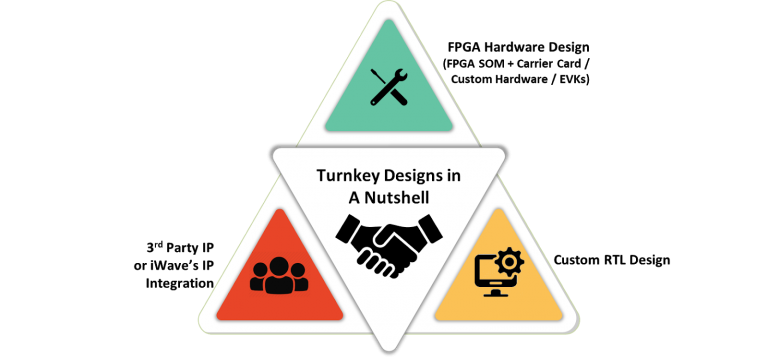

ターンキー製品設計会社として、お客様の仕様に合わせたFPGA設計を提供します。これには、RTL設計、iWaveまたはサードパーティIPコアのFPGA SOMへの統合、キャリアカード/カスタムハードウェア/既製評価キットが含まれ、低消費電力、高性能、最適化設計をターゲットとしたエンドツーエンドのソリューションを提供します。

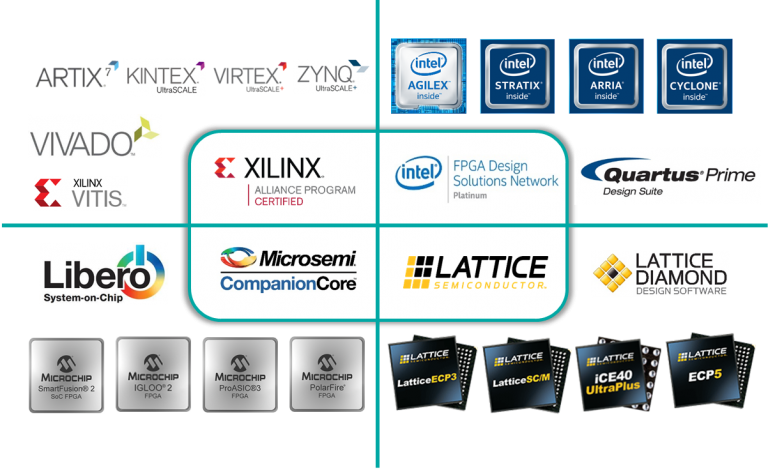

デバイスとEDAツールの合理化

ターンキーデザインサービス

iWave Systemsは、高速データ収集(ADC/DAC)、DSP、ビデオ処理、高速バスインターフェースとトランシーバーベースの設計、AI/MLアプリケーション、ASIC概念実証(POC)、事前・事後シリコン検証、数百万ゲートの複雑な設計などの分野のプロジェクトに幅広いFPGA開発専門知識を提供し、多様なスキルを持つFPGA設計チームによって、企業がリスク、コスト、設計サイクルを最小限に抑えるのを支援します。

FPGA設計サービスを提供するだけでなく、iWaveは実績のある、最適化された、使いやすい FPGA IPコアの広範なスイートを所有していることを誇りとしています: ARINC818コンプリート・スイート、ストレージ、ビデオ・プロセッシングIP、レガシーx86プロセッサーとそのペリフェラル。

カスタムFPGA設計

Requirement Analysis & Strategizing best market solution

Architecture blue-print using State-of-Art Design Methodologies

Implementation & Optimization for Area, Power, Timing & Resources

Simulation, Integration and Testing

RTL Coding: VHDL, Verilog & System Verilog

ハードウェア - ソフトウェア共同デザイン

Embedded Software Development for SoCs with Soft & Hard IP Cores

Complete Software Development Life Cycle (BSP, Driver, APIs, Application)

Algorithm Development in FPGAs using High-Level Synthesis – HLS Tools

Validation of whole package with in-house platforms viz. SOMs & EVKs

ASICプロトタイピング

Complete Life Cycle of a Chipset

Test Specification Capture, Platform Identification, RTL Porting

Code Coverage, Lint & CDC Checks

Pre-Silicon & Post Silicon Validation, Characterization

AIとML

Low Latency, High Performance, Better Accuracy

Running multiple CNNs simultaneously

Various CNNs scalable from Edge to Cloud

Frameworks: Caffe, TensorFlow, MX Net, Darknet

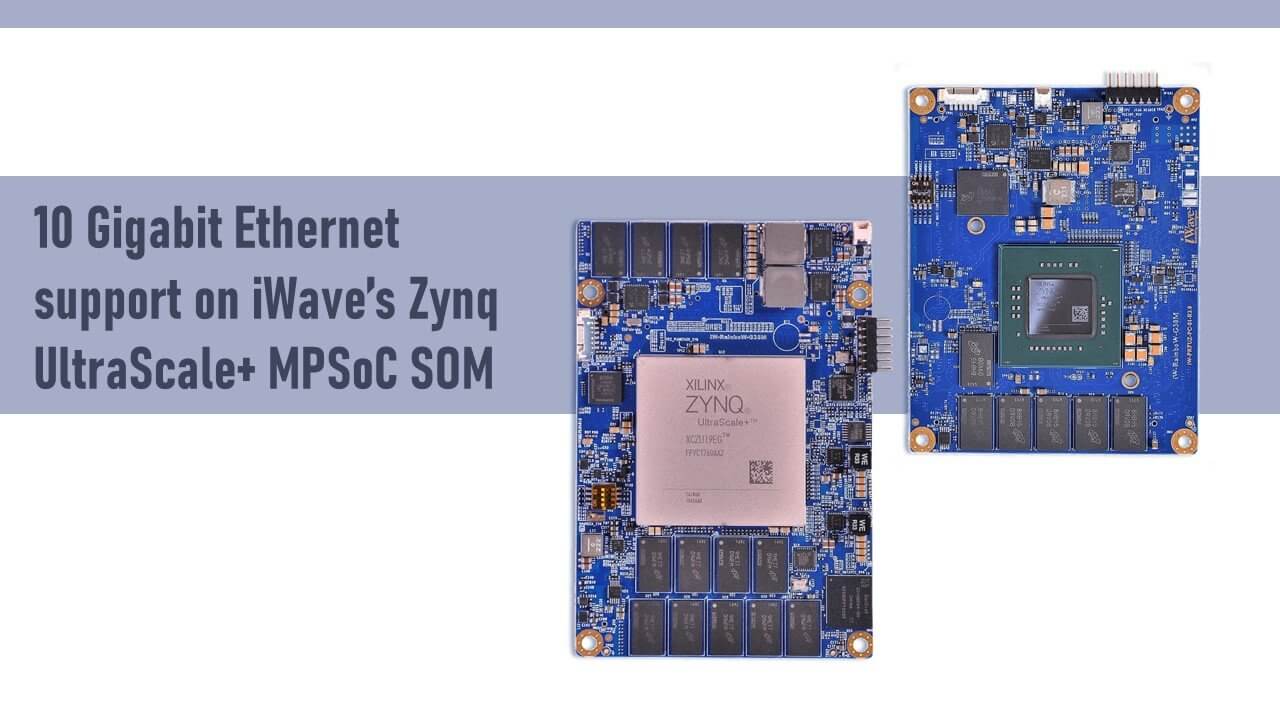

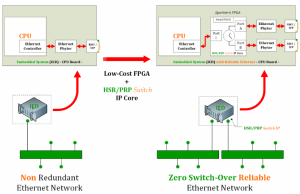

高速バス&トランシーバー・ソリューション

Maximum Performance, Low-Latency, Peak Bandwidth up to 25Gbps/ lane

Backplane, Board to Board, Mezzanine Card over Copper or Optical Medium

Protocol: ARINC818, sRIO, Aurora, PCIe, SATA, JESD204, USB, sFPDP, 10/25/40/100Gb

Memory: DDR 4/5, QDR, RLDRAM

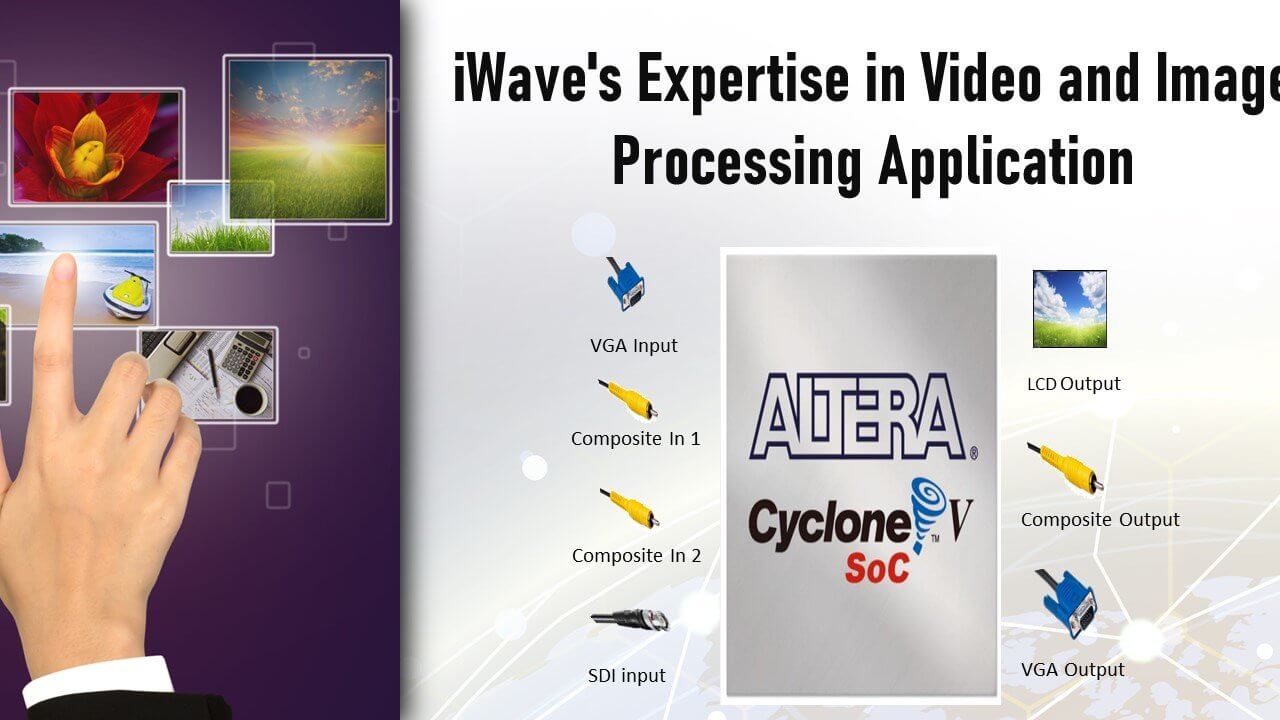

画像・映像処理

In-depth experience in working with Image & Video Processing like Chroma Resampler, De-Interlacer, Color Space Conversion, Alpha Blender, Mixer, Scalar, Color Correction & Enhancement, etc.,

Analog Video: STANAGRGB, CVBS, VGA, Composite

Digital Video: HDMI, SDI, Display Port, DVI, ARINC818