- 製品紹介

- 自動車

- 航空電子工学

FMCカード

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x16 FMC+モジュール

- PCIe Gen4 x16 FMC+モジュール

- PCIe Gen3 x8 FMCモジュール

- クアッド QSFP28 FMC+ モジュール

- PCIe Gen3 x8 FMCモジュール

- クアッド QSFP28 FMC+ モジュール

- FMCアドオンカード

- FMCアドオンカード

COTSモジュール

- Agilex 7 SmartNICカード

- Zynq RFSoC ADC DAC PCIeカード

- ZU7/ZU5/ZU4 PCIe SmartNIC Card

- ZU7/ZU5/ZU4 PCIe SmartNIC Card

- ZU19/17/11 PCIe SmartNICカード

- ZU19/17/11 PCIe SmartNICカード

- PCIe Switch Module

- PCIe to SD 3.0 M.2モジュール

- PCIe Switch Module

- PCIe to SD 3.0 M.2モジュール

- Kintex-7 PCIeカード

- Kintex-7 PCIeカード

- Zynq ZU7/ZU5/ZU4 3U-VPX

- Zynq ZU7/ZU5/ZU4 3U-VPX

- Virtex UltraScale+ 3U VPX

- Virtex UltraScale+ 3U VPX

- Kintex UltraScale+ 3U VPX

- Kintex UltraScale+ 3U VPX

- RFSoC 3U VPX

- RFSoC 3U VPX

- Agilex 9 3U VPX

- Zynq ZU19/17/11 3U VPX

- Zynq ZU19/17/11 3U VPX

- Kintex-7 3U VPXカード

- Kintex-7 3U VPXカード

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x16 FMC+モジュール

- PCIe Gen4 x16 FMC+モジュール

- PCIe Gen3 x8 FMCモジュール

- クアッド QSFP28 FMC+ モジュール

- PCIe Gen3 x8 FMCモジュール

- クアッド QSFP28 FMC+ モジュール

- FMCアドオンカード

- FMCアドオンカード

- IP Cores

- ODMソリューション

- カスタムデザイン

- Company

お見積もり

フォームにご記入ください!

アイウェーブにご連絡いただきありがとうございます。

担当者よりご連絡させていただきます!

お問い合わせ

アイウェーブにご連絡いただきありがとうございます。

担当者よりご連絡させていただきます!

ニュースレターのご購読ありがとうございます!

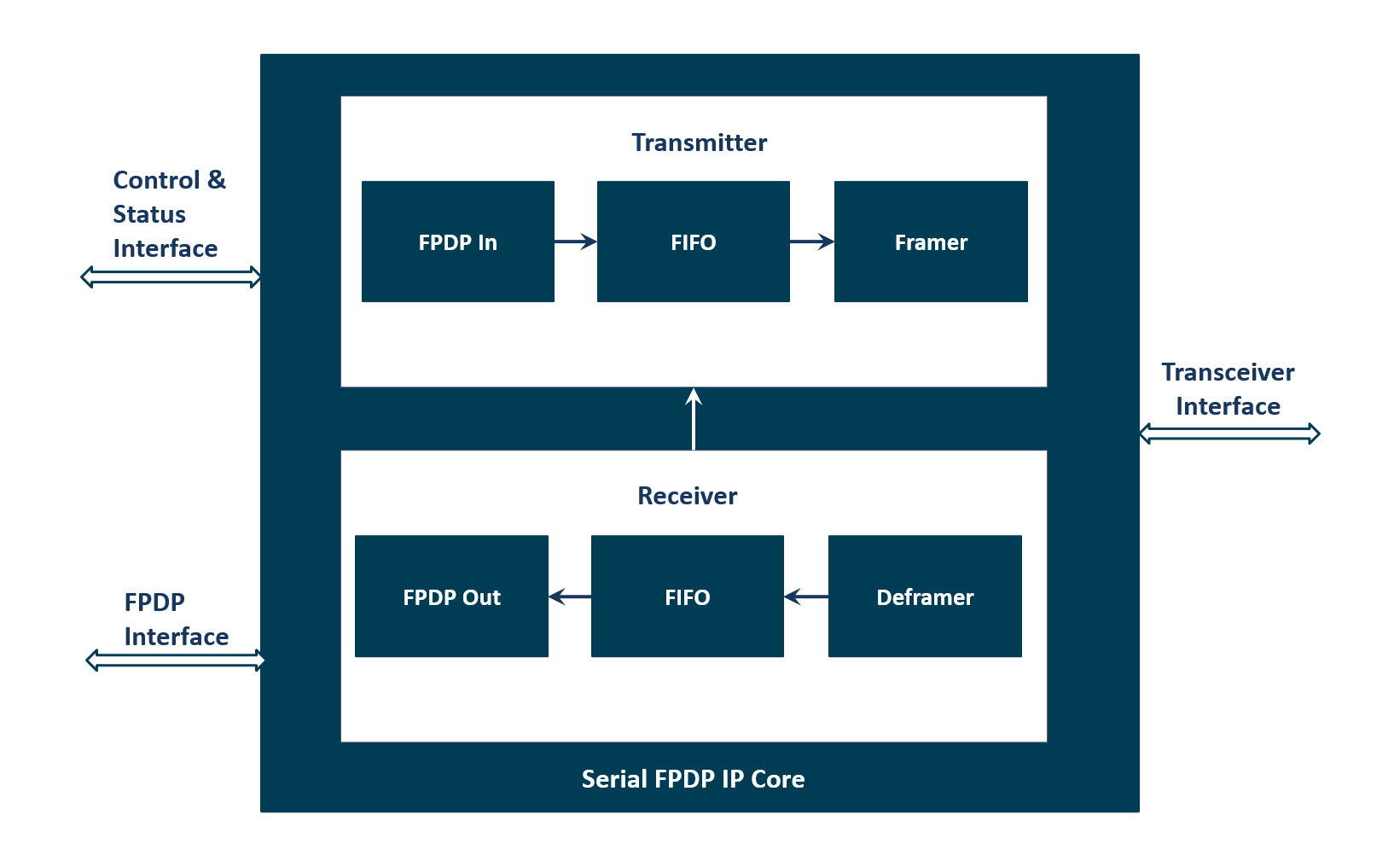

シリアルFPDP(sFPDP)

シリアルFPDP(sFPDP)

sFPDP IP Core is based on ANSI/VITA 17.1-2015 Standards. This IP core provides a relatively simple protocol using maximum available data throughput with a minimum protocol for point-to-point data links. sFPDP links support a wide range of physical interfaces with the most common option being 10 gigabits per second multimode fiber.

Categories: FPGA IP Cores, sFPDP IP Cores

仕様

- Compliant with ANSI/VITA 17.1-2015 Serial FPDP standard

- Supported link speeds

- Up to 10Gbuad

- Data Frames supported

- Unframed Data

- Single Frame Data

- Fixed Size Repeating Frame Data

- Dynamic Size Repeating Frame Data

- System Configurations supported

- Basic System Flow Control

- Bi-directional Data Flow

- Copy Mode

- Copy/Loop Mode

- Unidirectional support

- Optional flow control

- CRC

- Host-Bus interface

- Parallel FPDP

- Configurable parameters Transmit FIFO depth

- Receive FIFO depth

- Transmit FIFO watermark to assert SUSPEND output

- Transmit FIFO watermark for TX FIFO Overflow signal generation

- Receive FIFO watermark for STOP/GO signal generation

ハイライト

- Serial Front Panel Data Port (sFPDP) IP core for FPGA is based on the ANSI/VITA 17.1-2015 standard

- The Serial FPDP standard supports Up to 10Gbuad link speed.

関連ビデオ

関連商品

ダウンロード

Please fill in the form below to download the document.

ダウンロード・フォームへのご記入ありがとうございました。

Request Document

下記のフォームにご記入ください!

アイウェーブにご連絡いただきありがとうございます。

担当者よりご連絡させていただきます!