Corazon-AIでXILINX FPGAのエッジインテリジェンスを解き放つ

高まるEdgeAIのニーズ

従来、人工知能ソリューションは、データのフィルタリング、刈り込み、計算のほとんどをクラウド上で行い、クラウドに依存してきた。現在、産業界やスマートシティでは、エッジでの意思決定と計算によるリアルタイムの先制行動が求められている。

業界や業種を問わず、人工知能ソリューションではスピードとプライバシーが重要なパラメータとなり、エッジのテクノロジー選択に影響を与えている。医療用画像処理からインテリジェントな交通管理まで幅広いアプリケーションにおいて、ハードウェアの高速化とレイテンシの低減を特徴とする高性能インテリジェント・デバイスが必要とされています。

EdgeAIデバイスの高まる要件とエッジ上のFPGAの強力な提案に応えるため、アイウェーブはXilinx Zynq® UltraScale+™ MPSoCを中心に構築されたエッジAIソリューションであるCorazon-AIを発表しました。

FPGA、GPU、CPU上のAIエンジン

CPUコア上のAIエンジンを最大限に活用するために、周波数スケーリングが採用され、高速化が達成された。これはプログラマーにとって、マルチコアプラットフォームをターゲットにしてモデルを最適化するという課題だった。このため、AIエンジンを統合するための大規模な並列アレイ・ソリューションを提供するGPUが登場した。

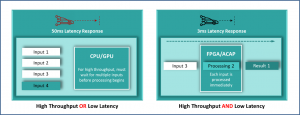

スループットの達成は、処理に取り掛かる前にすべての入力を待つ高バッチサイズと相まって、レイテンシの増加に道を開く。GPUソリューションでは性能とレイテンシーの妥協があり、開発者は難しい決断を迫られます。FPGA上のAIエンジンは、より多くの並列性を提供し、AIエンジンの能力を高めると同時に、バッチ・サイズを縮小してより優れた処理能力を達成する。したがって、FPGAは性能とレイテンシーの妥協点を解決することができます。

AIエンジンはFPGA上で動作するが、処理機能はベース・ロジック・ポート・レベルでカスタマイズできる。 このコンフィギュレーションにより、内部バス構造による差し迫ったレイテンシなしに、ハードウェアI/Oへの直接アクセスが可能になります。これにより、特別なハードウェア・インターフェースからのデータを即座に高レイテンシで処理し、入力データに対してリアルタイムでアクションを実行できる。これにより、FPGAの応答性が向上し、より専用的な特殊用途の革新操作が可能になります。

したがって、柔軟性、レイテンシー、パフォーマンス、最適化を分析すると、FPGAがトップランナーであり、エッジでのAIに理想的であると考えられる。

コラソン -AI - AIの心臓部

Corazon-AIは、DPU(Deep Learning Processor Unit)と呼ばれるザイリンクスのFPGA AIエンジンを内蔵し、AIアプリケーションのアクセラレーションを行います。DPUは、畳み込みニューラルネットワーク専用に最適化されたコンフィギュレーション可能な計算エンジンです。

Corazon-AIは、8台のIPカメラ、複数のUSBカメラ、SDIカメラに接続できるインターフェースを持っています。内蔵のAI推論エンジンによってプロアクティブに処理されるマルチアングルの高解像度ビデオフレームをキャプチャする機能は、さらなる強みを加える。

デュアル・ギガビット・イーサネットなどの高速接続や、Wi-Fi、ブルートゥース、携帯電話接続などの複数のワイヤレス接続オプションをサポートすることで、このデバイスは必要に応じてクラウドやサーバーと通信することができ、モジュール式のアーキテクチャを採用している。

Corazon-AIの理想的なアプリケーションは、インテリジェントな料金管理システムである。8台のIPカメラを接続することで、レーンをまたぐカメラが個々の画像やビデオストリームをキャプチャし、各入力ストリームで同時にモデルを実行することができる。意思決定とデータ・フィルタリングはエッジで行うことができ、各料金所で複数のゲートウェイを持つ必要がなくなる。 現在のところ、ビデオストリーム全体が料金所からコントロールセンターに転送され、そこで意思決定と処理が行われている。

Corazon-AIは、交通管理、ビデオ監視、スマートパーキング、自動ビデオ検査ソートなど、複数のカメラを接続する必要があり、エッジでコンピューティングやデータ駆動型の意思決定を行う必要があるアプリケーションに理想的に適合します。

DPUは高スループットと低レイテンシーを実現します:

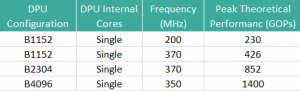

DPUは設定可能なハードウェアアーキテクチャ(B512、B800、B1024、B1152、B1600、B2304、B3136、B4096)を備えています。 各DPUアーキテクチャは最大3つの内部コアを構成できます。 また、命令アクセス、コンフィギュレーションアクセス、データアクセス用に専用のAXIインターフェースが用意されています。データアクセスAXIマスターインターフェースは、コンボリューション、デコンボリューション、デプスワイズコンボリューションが可能な64ビットまたは128ビットの幅をサポートしています。

図1:DPUの理論上のピーク性能の構成による違い。

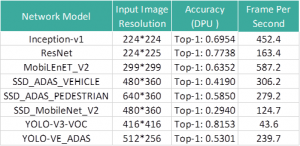

図2:複数のモデルのパフォーマンス

*これらのモデルは、XILINXのプルーニングツールを使用してプルーニングされています。

* 精度は8ビット固定量子化に基づいています。

* シングルB4096コア、16スレッドのCorazon-AIプラットフォームで測定

iWave Systems Technologies Pvt. Ltd.について

iWave Systems社について: 1999年に設立されたiWave Systems Technologies Pvt. Ltd.は、組み込みハードウェアおよびソフトウェア、FPGAの設計および開発を含む製品エンジニアリングサービスに注力しています。FPGAに関して18年以上の経験を有し、カスタム設計サービスやXILINX System on Modules - ZYNQ 7000シリーズおよびUltra Scale+ MPSoCシリーズを幅広く提供しています。

お問い合わせや詳細については、mktg@iwavesystems.comまでご連絡ください。