# Kintex-7 Based SATA 3.0 Host Controller IP Integration Manual

# **Table of Content**

| 1 I | INTRODUCTION                                    |    |

|-----|-------------------------------------------------|----|

| 1.1 |                                                 |    |

| 1.2 |                                                 |    |

| 1.3 |                                                 |    |

| 2 S | ATA 3.0 HOST CONTROLLER                         | 6  |

| 1   |                                                 | 6  |

|     | SATA FMC Daughter Card                          |    |

| 3 I | P CONFIGURATION AND INSTANTIATION               | 7  |

| 3.1 | Example Design                                  | 7  |

| 3.2 |                                                 |    |

| 3.3 |                                                 |    |

| 3.4 |                                                 |    |

| 3.5 |                                                 |    |

| 4 I | MPLEMENTATION DETAILS                           | 18 |

| 4.1 | CLOCK DOMAIN                                    | 18 |

| 4.2 |                                                 |    |

| 5 D | DESIGN MODIFICATION TO BE DONE FOR CUSTOM BOARD | 19 |

| 6 R | RESOURCE UTILIZATION                            | 20 |

|     |                                                 |    |

# **List Of Figures**

| Figure 1: SATA 3.0 Host Controller setup                                | 6  |

|-------------------------------------------------------------------------|----|

| Figure 2: SATA FMC Daughter Card                                        | 6  |

| Figure 3: Instantiation Module of SATA 3.0 Host Controller Block design | 8  |

| Figure 4: SATA 3.0 Host Controller Block Design Configuration step 1    | 8  |

| Figure 5: SATA 3.0 Host Controller Block Design Configuration step 2    | 9  |

| Figure 6: SATA 3.0 Host Controller Block Design Configuration step 3    | 10 |

| Figure 7: SATA 3.0 Host Controller Block Design Configuration step 4    | 10 |

| Figure 8: SATA 3.0 Host Controller Block Design Configuration step 5    | 11 |

| Figure 9: Instantiation of SATA 3.0 Host Controller Block Design        | 11 |

| Figure 10: Instantiation Module of GTH Transceiver wizard               | 12 |

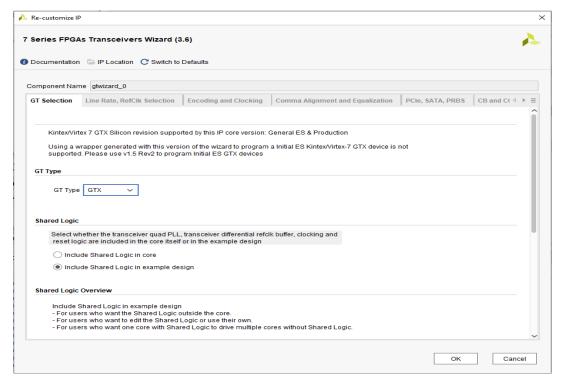

| Figure 11: GTX Transceiver Configuration step 1                         | 13 |

| Figure 12: GTX Transceiver Configuration step 2                         | 14 |

| Figure 13: GTX Transceiver Configuration step 3                         | 14 |

| Figure 14: GTX Transceiver Configuration step 4                         | 15 |

| Figure 15: GTX Transceiver Configuration step 5                         | 16 |

| Figure 16: GTX Transceiver Configuration step 6                         |    |

| Figure 17: Instantiation of GTX transceiver wizard (i)                  | 17 |

| Figure 18: Instantiation of GTX transceiver wizard (ii)                 | 17 |

| Figure 19: Constraints of SATA 3.0 Host Controller                      | 18 |

|                                                                         |    |

# **List Of Tables**

| Table 1: Acronyms & Abbreviations                                  | 5 |

|--------------------------------------------------------------------|---|

| Table 2 :Resource Utilization for Kintex-7 Development Kit device. |   |

## 1 Introduction

# 1.1 Purpose

The purpose of this document is to describe the details of SATA 3.0 Host Controller Integration with Kintex-7 Development kit.

#### 1.2 Overview

SATA 3.0 Host Controller interfaces the Micro blaze Processor through AXI4-Bus enabling the data transfers between each other. The Micro blaze Processor will send the response to the GPIO's depending on the command issued.

## 1.3 Acronyms & Abbreviations

**Table 1: Acronyms & Abbreviations**

| Term | Meaning                       |

|------|-------------------------------|

| FPGA | Field Programmable Gate Array |

| GPIO | General purpose input output  |

| FMC  | FPGA Mezzanine Card           |

| LUT  | Look Up Table                 |

| IO   | Input and Output              |

| FF   | Flip Flop                     |

# 2 SATA 3.0 Host Controller

The below figure represents the test setup for the Kintex-7 Development Board with SATA FMC Daughter card and Intel SSD Device.

Figure 1: SATA 3.0 Host Controller setup

## 2.1 SATA FMC Daughter Card

Figure 2: SATA FMC Daughter Card

# 3 IP Configuration and Instantiation

### 3.1 Example Design

The SATA 3.0 Host Controller example design mainly consists of

- Test Driver: Test Driver responsible for issuing commands for read and write operations towards through the transport layer. And its responsible for overall command execution, including control of Register accesses.

- 2. **Micro blaze processor:** Micro blaze Processor is used to configure GPIO through the AXI-4 Interconnect mainly access to read and write operation to the device.

- 3. **Transport Layer:** The Transport layer is responsible for placing control information and data to be transferred between the host and device in a packet/frame, known as a Frame Information Structure (FIS).

- 4. **Link Layer:** The Link layer is responsible for taking data from the constructed frames, scramble or de-scramble and perform CRC check.

- 5. **Physical Layer:** The Physical layer is responsible for transmitting and receiving the (8B/10B) encoded information as a serial data stream on the line. This layer consists of 3 blocks. That was Speed negotiation, Transceiver wizard, OOB signaling and control.

- a. **GTX Transceiver wizard:** responsible for highspeed serial communication in the physical layer.

- b. **Speed negotiation:** responsible for changing the line rate (Ex: 6GB/s to 3GB/s).

- c. **OOB signaling:** responsible for OOB signal generation and detection, provide status to link layer.

#### 3.2 SATA 3.0 Host Controller IP Instantiation

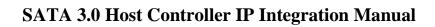

The SATA 3.0 Host Controller block design (Micro.v) is instantiated in the design as shown in the below Figure 3.

Figure 3: Instantiation Module of SATA 3.0 Host Controller Block design

Module sata\_top was the top module of the project which integrates with physical layer, link layer, transport layer, test driver along with SATA 3.0 Host Controller module.

## 3.3 Steps to Configuring the SATA 3.0 Host Controller

- Install the required Vivado Design Suite for the host PC adding the license path.

Downloads (xilinx.com)

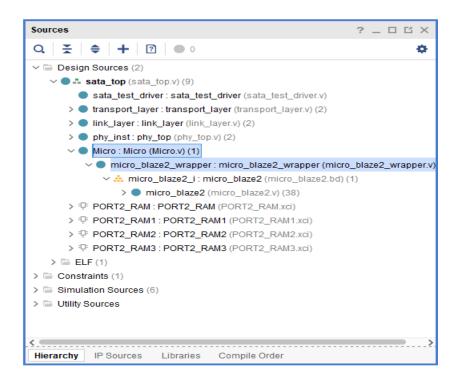

- Open the SATA 3.0 Host Controller project. Go to the Flow navigator → Project Manager

→ IP Integrator → open "Create Block design".

- Then give block design name (micro\_blaze2) and directory as E:\ASCDO\Projects\SATA\_3.0\_KC705\_20\_1\gtwizard\_0\_example.srcs\sources\_1\bd\mi cro\_blaze2/ micro\_blaze2.bd in the below Figure 4.

Figure 4: SATA 3.0 Host Controller Block Design Configuration step 1

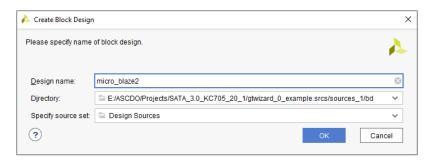

• Diagram and Address Editor windows will be opened. In Diagram window, click '+' to add the IP into the block deign. What is the required IP need for the design that should be added.

Figure 5: SATA 3.0 Host Controller Block Design Configuration step 2

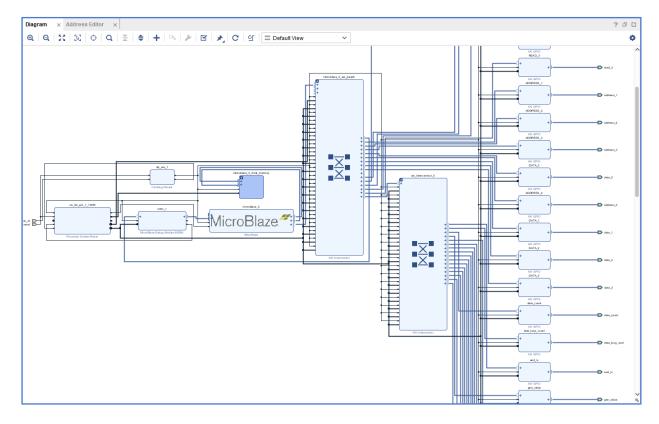

After adding IP like Micro blaze, processor system reset, AXI4-interconnect, Micro blaze

Debug Module, clocking wizard and GPIO, the required GPIO's are connected to the Micro

blaze by using AXI4-stream interconnect to the block design as per shown in below Figure

6. Micro blaze was configured by as per the SATA design requirements.

#### Figure 6: SATA 3.0 Host Controller Block Design Configuration step 3

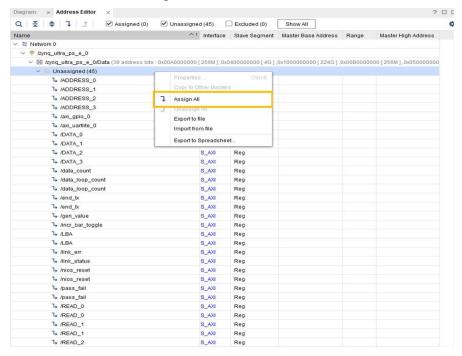

• Once the block design was created, then go to Address Editor window to assign the address to all the GPIO's as shown in Figure 7.

Figure 7: SATA 3.0 Host Controller Block Design Configuration step 4

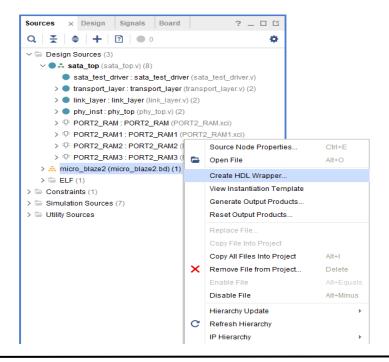

• Synthesize the block design first by validating the design (press key 'F6') and generate the outputs. Once the design validation was completed then generate wrapper module of the block design by right click the .bd file and click Create HDL wrapper as shown in Figure

8. After the wrapper file creation then Instantiate inside the top module of design as shown in Figure 3.

Figure 8: SATA 3.0 Host Controller Block Design Configuration step 5

• And the Micro file instantiation inside the sata\_top module as shown in Figure 9.

```

Micro Micro (

address_0_export ( address_0_export ),

address_1_export ( address_1_export ),

address_1_export ( address_2_export ),

address_3_export ( address_3_export ),

address_3_export ( address_3_export ),

clock_rtl ( EXT_USR_CLK_0 ),

data_0_export ( data_0_export ),

data_1_export ( data_1_export ),

data_2_export ( data_2_export ),

data_3_export ( data_3_export ),

end_tx_export ( end_tx ),

incr_bar_toggle_export ( incr_bar_toggle ),

iner_bar_toggle_export ( pass_fail ),

ren_0_export ( rden_0_export ),

ren_0_export ( rden_0_export ),

ren_1_export ( rden_1_export ),

rest_lexport ( rden_3_export ),

rest_reset_n ( rsy_reset_n_i ),

sata_oper_export ( sata_oper ),

start_tx_export ( sata_oper ),

start_tx_export ( uart_rxd ),

uart_rxd ( uart_rxd ),

uart_rxd ( uart_txd ),

inls_status_export ( data_count ),

data_loop_count_export ( data_count ),

data_loop_count_export ( data_loop_count ),

inlh_err_export ( fuine_clk )

inico_clk ( micro_clk )

```

Figure 9: Instantiation of SATA 3.0 Host Controller Block Design

#### 3.4 GTX transceiver IP Instantiation

Create one example design of GTX Transceiver wizard as per SATA the protocol in the Vivado. And configure GTX Transceiver wizard settings as per design. Then instantiate the example design of GTX Transceiver wizard to the physical layer module as shown in below Figure 10.

Figure 10: Instantiation Module of GTH Transceiver wizard

The Figure 10 represents the gtwizard\_0\_support.v module of GTX Transceiver wizard instantiated inside the physical layer module (phy\_top).

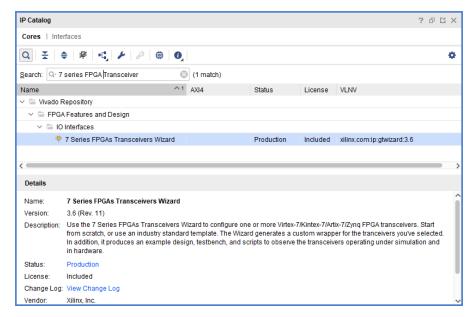

# 3.5 Steps to Configure the GTH Transceiver IP

Go to the Flow navigator → Project Manager → IP Catalog. In IP catalog, add the required

7 series FPGA Transceiver wizard as shown in below Figure 11.

Figure 11: GTX Transceiver Configuration step 1

After that 7 series FPGA Transceiver wizard (3.6) will be opened and set the transceiver configuration GT type as "GTX". And configure the GTX-Transceiver wizard IP as per SATA 3.0 Host Controller design. The Line rate, RefClk selection and PLL type and rest of the settings should be configured as per the design.

Figure 12: GTX Transceiver Configuration step 2

Once the configuration was completed, then generate outputs of GTX Transceiver wizard.

After right click on the GTX Transceiver wizard to open the IP example design.

Figure 13: GTX Transceiver Configuration step 3

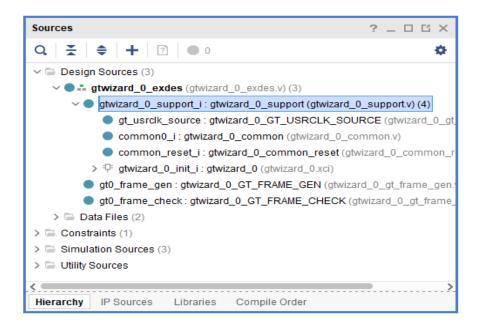

• Give the path as E:\ASCDO\Projects\SATA\_3.0\_KC705\_20\_1\gtwizard\_0\_ex for open the example design of GTX Transceiver wizard. The Example design of GTX Transceiver wizard was containing gtwizard\_0\_exdes and other modules.

Figure 14: GTX Transceiver Configuration step 4

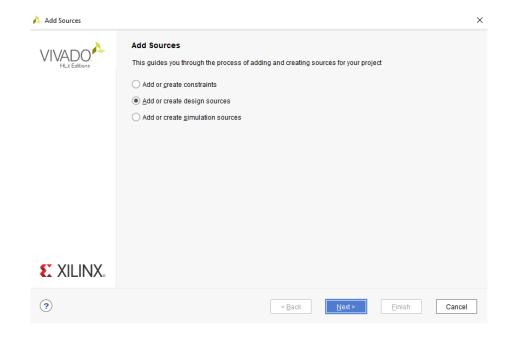

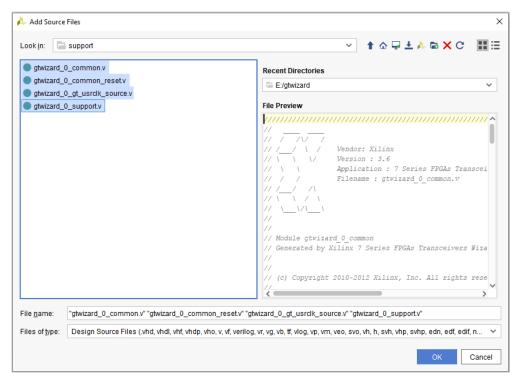

• Then go to the SATA 3.0 Host Controller design, right click the "+" inside the source window and give "Add or create design sources". Then go to Add files → gtwizard\_0\_ex → imports.

#### Figure 15: GTX Transceiver Configuration step 5

Add the support.v module and required modules of GTX Transceiver wizard to the SATA 3.0 Host Controller design.

Figure 16: GTX Transceiver Configuration step 6

• And the gtwizard\_0\_support instantiation of GTX Transceiver wizard inside the phy\_top module as shown in Figure 17.

```

gtwizard_0_support #

.EXAMPLE_SIM_GTRESET_SPEEDUP ( "TRUE" ),

.STABLE_CLOCK_PERIOD ( 16

gtwizard_0_support_i

( sys_reset_i || reset_tx

( sys_reset_i || reset_tr

.soft_reset_tx_in

.soft_reset_rx_in

( sys_reset_i || reset_tx

.dont_reset_on_data_error_in ( 1'b0

.q3_clk0_gtrefclk_pad_n_in ( Q3_CLK1_GTREFCLK_PAD_N_IN ), .q3_clk0_gtrefclk_pad_p_in ( Q3_CLK1_GTREFCLK_PAD_P_IN ),

( 1'b1

.gt0_data_valid_in

.gt0_txusrclk_out

.gt0 txusrclk2 out

( tx_std_clkout_o

.gt0_rxusrclk_out

.gt0_rxusrc1k2_out

( rx_std_clkout_o

.gt0_cpllreset_in

( l'b0

.gt0 rxrate in

( tx rate d2

.gt0 eyescanreset in

( 1'h0

.gt0_rxuserrdy_in

( 1'h0

.gt0_eyescantrigger_in

( 1'h0

.gt0_rxdata_out

( rx_parallel_data

.gt0_gtxrxp_in

( RXP IN

.gt0_gtxrxn_in

( RXN IN

( 1'h0

.gt0_rxdfelpmreset_in

.gt0_rxmonitorsel_in

( 2'h0

.gt0_gtrxreset_in

( 1'b0

.gt0_rxcomwakedet_out

( rx_comwake_det

```

Figure 17: Instantiation of GTX transceiver wizard (i)

```

.gt0_rxcominitdet_out ( rx_cominit_det ),

.gt0_rxelecidle_out ( rx_elecidle ),

.gt0_rxcharisk_out ( rx_datak ),

.gt0_rxresetdone_out ( gt0_rxresetdone ),

.gt0_gttxreset_in ( 1'b0 ),

.gt0_txelecidle_in ( tx_std_elecidle ),

.gt0_txrate_in ( tx_rate ),

.gt0_txrate_in ( tx_rate ),

.gt0_gtxxn_out ( TXN_OUT ),

.gt0_gtxtxn_out ( TXP_OUT ),

.gt0_gtxtxp_out ( tx_datak ),

.gt0_txcharisk_in ( tx_datak ),

.gt0_txresetdone_out ( gt0_txresetdone ),

.gt0_txcominit_in ( tx_cominit ),

.gt0_txcomwake_in ( tx_comwake ),

.sysclk_in ( sysclk_in_o ),

.tx_rate ( tx_rate ),

.gen_value ( gen_value ),

.RXCDROVRDEN_i ( RXCDROVRDEN_i ),

.debug1 ( debug2 ),

.debug2 ( debug2 ),

```

Figure 18: Instantiation of GTX transceiver wizard (ii)

- The Constraint file (.xdc) provided in the design is for Xilinx Kintex-7 development Board and should be changed for custom boards.

- Give the required clock, Pin/IO constraints for SATA 3.0 Host Controller in the .xdc file and compile the custom design with SATA 3.0 Host Controller IP.

# **4 Implementation Details**

#### 4.1 Clock Domain

In SATA 3.0 Host Controller, the actual system clock (EXT\_USR\_CLK\_P) was 200MHz and it was coming from the Kintex-7 Development kit. The transceiver reference clock (TILE0\_REFCLK\_PAD\_P\_IN) was 150MHz and transceiver system clock was 156.25MHz. The gt0\_txusrclk2\_out clock of GTX transceiver wizard was used to the input clock of all other modules of SATA 3.0 Host Controller design.

#### 4.2 Constraints

Figure 18 shows the pin constraints in the .xdc file of SATA 3.0 Host Controller design

```

create clock -period 5.000 [get ports EXT_USR_CLK_P]

create clock -period 6.667 [get_ports TILEO_REFCLK_PAD_P_IN]

create clock -period 6.400 [get ports sysclk_p_i]

##################################### Constraints KC705##########################

set_property PACKAGE_PIN AB7 [get_ports sys_reset_n_i]

set property PACKAGE_PIN K28 [get ports sysclk_p_i]

set property PACKAGE_PIN AD12 [get ports EXT_USR_CLK_P]

set property PACKAGE_PIN M19 [get_ports uart_rxd]

set property PACKAGE_PIN K24 [get_ports uart_txd]

set property PACKAGE_PIN AB8 [get ports led_degl]

set property PACKAGE_PIN AA8 [get ports led_deg2]

set property PACKAGE_PIN C8 [get_ports TILEO_REFCLK_PAD_P_IN]

set property PACKAGE_PIN E4 [get_ports RXP0_IN]

set property IOSTANDARD DIFF SSTL15 [get ports EXT USR CLK P]

set property IOSTANDARD DIFF_SSTL15 [get ports sysclk p i]

set property IOSTANDARD LVCMOS15 [get ports sys_reset_n_i]

set property IOSTANDARD LVCMOS25 [get ports uart_rxd]

set property IOSTANDARD LVCMOS25 [get ports uart_txd]

set property IOSTANDARD LVCMOS15 [get ports led_deg1]

set property IOSTANDARD LVCMOS15 [get ports led_deg2]

```

Figure 19: Constraints of SATA 3.0 Host Controller

# 5 Design modification to be done for Custom Board

- Update the FPGA part number/board according to the FPGA device used

- Update the complete design for the selected FPGA device

- Updated the Transceiver wizard for the selected board.

- Update the pin constraints for SATA interface, clock, reset and UART pins

- Update the clock constraint according to the input clock frequency for the selected FPGA device

- Recompile the design to generate the new binaries and use the XSA file to create the new application project in Vitis

# **6 Resource Utilization**

The table below shows the resource utilization summary for Kintex-7 development kit for SATA 3.0 Host Controller IP.

Table 2: Resource Utilization for Kintex-7 Development Kit device.

| Resource | Utilization | Available |

|----------|-------------|-----------|

| LUT      | 14055       | 203800    |

| LUTRAM   | 1646        | 64000     |

| FF       | 18813       | 407600    |

| BRAM     | 91          | 445       |