# NAND Flash Controller Integration Manual

# **Table of Contents**

| 1 IN | NTRODUCTION                       | 5  |

|------|-----------------------------------|----|

| 1.1  | Purpose                           | 5  |

| 1.2  |                                   |    |

| 1.3  | REFERENCE DOCUMENT                |    |

|      | Overview                          |    |

| 1.5  | ACRONYMS AND ABBREVIATIONS        | 6  |

| 2 IF | P CONFIGURATION AND INSTANTIATION | 7  |

| 2.1  | Example design                    | 7  |

|      | IP Configuration                  |    |

| 2.3  | STEPS TO INSTANTIATE NAND HOST IP | 9  |

| 3 IN | MPLEMENTATION DETAILS             | 13 |

| 3.1  | PARAMETER SETTINGS                | 13 |

| 3.2  | Constraints                       | 13 |

| 4 F  | PGA IMPLEMENTATION                | 15 |

| 4.1  | RESOURCE UTILIZATION              | 15 |

# **List of Figures**

| Figure 1: NAND Flash Controller Block Diagram                                         | 5  |

|---------------------------------------------------------------------------------------|----|

| Figure 2: Block Design Modules of the example design project                          | 7  |

| Figure 3: Assign Specific Addresses & Range to ports                                  | 8  |

| Figure 4: nand_host.edn(netlist file)is instantiated in Nand Flash Host Controller IP | 8  |

| Figure 5: Top Module for the example design                                           | 9  |

| Figure 6: Click on "Open Project"                                                     | 10 |

| Figure 7: Adding NAND Flash Controller IP to the IP repository                        | 10 |

| Figure 8: Adding the NAND Flash Controller IP to the block design                     | 11 |

| Figure 9: Generate output products                                                    | 11 |

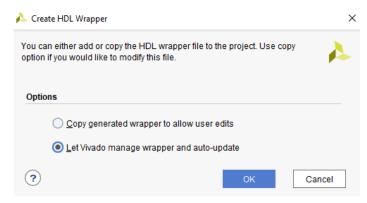

| Figure 10: Create HDL wrapper                                                         |    |

| Figure 11: Instantiation of NAND Host IP in NAND Flash Controller module              |    |

| Figure 12: Pin Constraints in example design xdc file                                 | 14 |

# **List of Tables**

| Table 1: Acronyms & Abbreviations                                     | 6  |

|-----------------------------------------------------------------------|----|

| Table 2: Device Utilization Summary for NAND Flash Host Controller IP | 15 |

## 1 Introduction

#### 1.1 Purpose

The purpose of this document is to describe NAND Flash Controller IP Integration details.

#### 1.2 Scope

This document describes the NAND Flash Controller IP and provides information about IP integration details.

#### 1.3 Reference Document

- NAND Flash Memory Datasheet

<a href="https://www.mouser.in/datasheet/2/671/micron\_technology\_micts06235-1-1759187.pdf">https://www.mouser.in/datasheet/2/671/micron\_technology\_micts06235-1-1759187.pdf</a>

- Open NAND Flash Interface Specification

- AMBA® AXITM and ACETM Protocol Specification

#### 1.4 Overview

Figure 1: NAND Flash Controller Block Diagram

NAND Flash Controller defines a standard register set for control and status of the NAND device. iWave Supplies NAND Flash Controller as standalone component in addition to Verilog modules

## 1.5 Acronyms and Abbreviations

**Table 1: Acronyms & Abbreviations**

| Term | Meaning                       |  |  |  |

|------|-------------------------------|--|--|--|

| AXI  | Advanced eXtensible Interface |  |  |  |

| FPGA | Field Programmable Gate Array |  |  |  |

| DDR  | Double Data Rate              |  |  |  |

| HDL  | Hardware Description Language |  |  |  |

| IP   | Intellectual Property         |  |  |  |

| irq  | Interrupt                     |  |  |  |

| ns   | Nano seconds                  |  |  |  |

| PL   | Programmable Logic            |  |  |  |

| PS   | Processor System              |  |  |  |

| RTL  | L Register Transfer Logic     |  |  |  |

| SoC  | System On Chip                |  |  |  |

| us   | Micro Seconds                 |  |  |  |

## 2 IP Configuration and Instantiation

#### 2.1 Example design

The NAND flash IP example design mainly consists of,

- 1. **NAND HOST IP:** NAND HOST IP is the design under test and controls the access to the external NAND chip based on the inputs from register set module.

- **2. NAND Wrapper:** This module accepts the commands and data over AXI 4 memory mapped interface and translates them to the user interface of NAND Host

- **3. NAND Register Set:** This module implements register set required for NAND Device control and status information

#### Note:

- Example design is compiled for XC7Z020CLG400-1 device with Vivado 2020.1 version.

- Example design currently supports dual die.

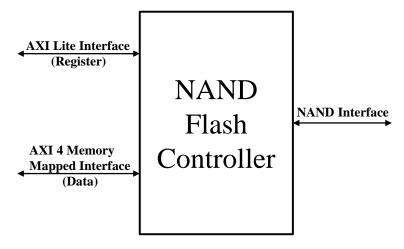

An example design project is created using Vivado 2020.1, at location ...\iW-EMFEW-Release-1.0\iW- EMFEW -Release-1.0\iW- EMFEW -PF-01-R1.0-REL1.0\iW- EMFEW -FF-01-R1.0\iW- EMFEW -SY-01-R1.0-REL1.0\iW\_ EMFEW \_ED. The design units that make the Block Design are shown in the figure below:

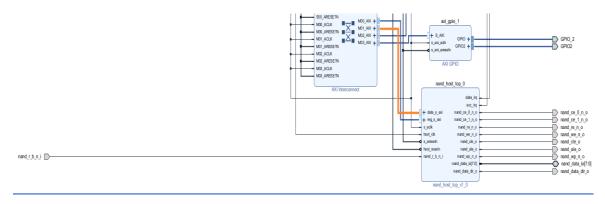

Figure 2: Block Design Modules of the example design project

Note: Change the assigned addresses in Address Editor tab present along with the block design/Diagram as below

1) For the register access: reg\_axi port assign 0x6800\_000 as address and range to 8M

# 2) For the data transfer: data\_axi port assign $0x5000\_0000$ as address and range to 128M

| 1 /nand_host_top_0 | data_s_axi | reg0 | 0x5000_0000 | 0 | 128M | * | 0x57FF_FFFF |

|--------------------|------------|------|-------------|---|------|---|-------------|

| 1 /nand_host_top_0 | reg_s_axi  | reg0 | 0x6800_0000 | 0 | 8M   | * | 0x687F_FFFF |

Figure 3: Assign Specific Addresses & Range to ports

### 2.2 IP Configuration

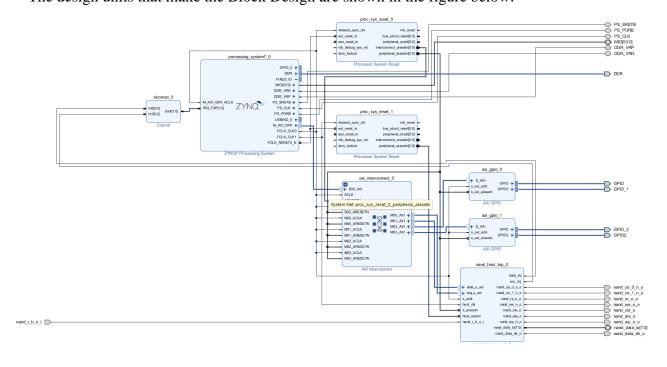

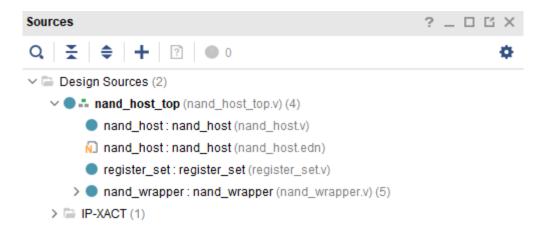

The Nand Flash Host Controller IP includes the netlist file i.e. nand\_host.dcp along with nand host.v(stub file),register set and nand wrapper in the design as shown in the figure below

Figure 4: nand\_host.edn(netlist file)is instantiated in Nand Flash Host Controller IP

Top Module of the Example design project is named as the top\_test\_module

Create a top module as shown in Figure below

```

module top test module

// system clocks

input wire sys clk p, //50mhz clock

//PS DDR Signals

inout wire [14:0] DDR_addr,

inout wire [2:0] DDR_ba,

inout wire DDR_cas_n,

inout wire DDR_ck_n,

inout wire DDR_ck_p,

inout wire DDR_cke,

inout wire DDR_cs_n,

inout wire inout wire [3:0] DDR_cs_n, inout wire [3:0] DDR_dm, inout wire [3:0] DDR_dq, inout wire [3:0] DDR_dqs_n, inout wire inout wire DDR_ras_n, inout wire DDR_ras_n, inout wire DDR_reset_n, inout wire DDR_VRN, inout wire DDR_VRN, DDR_VRP,

// PS MIO Signals

inout wire [53:0] MIO,

inout wire PS_CLK, inout wire PS_PORB, inout wire PS_SRSTE

PS_SRSTB,

inout wire

//FMC loopback

inout wire gpio_tri_io,

inout wire gpio_1_tri_io,

inout wire gpio_2_tri_io,

inout wire gpio2_tri_io,

//NAND Flash Interface

);

```

Figure 5: Top Module for the example design

## 2.3 Steps to Instantiate NAND HOST IP

• Install the required Vivado Design Suite 2020.1 for the host PC adding the license path. https://www.xilinx.com/support/download/index.html/content/xil%09%09inx/en/downloadNav/vivado-design-tools/archive.html

- Copy the project from ...\iW-EMFEW-Release-1.0\iW- EMFEW -Release-1.0\iW- EMFEW -PF-01-R1.0-REL1.0\iW- EMFEW -FF-01-R1.0\iW- EMFEW -SY-01-R1.0-REL1.0\iW\_ EMFEW \_ED" to your project directory in the host PC

- Open the Vivado 2020.1 and click on "Open Project" as shown in the below figure and select the required project from the folder by clicking ok

Figure 6: Click on "Open Project"

- Now the project selected will be opened in Vivado Design Suite 2020.1

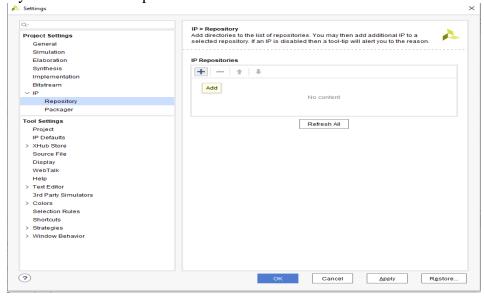

- Go to settings of Vivado 2020.1 and add the IP to the Project Settings → IP →

Repository→then add the IP path.

Figure 7: Adding NAND Flash Controller IP to the IP repository

IP location is ...\iW-EMFEW-Release-1.0\iW- EMFEW -Release-1.0\iW- EMFEW -PF-01-R1.0-REL1.0\iW- EMFEW -FF-01-R1.0\iW- EMFEW -SY-01-R1.0-REL1.0\iW\_

EMFEW \_ED \iW\_nand\_host. Add IP by clicking on the + sign as shown in above Figure. After the IP is added click on Apply,OK and close the dialogue box

Once the IP is added in the project repository, click on open block design present at the left most side of the Vivado 2020.1 tool.

1. After adding the other IP's as shown in the block design of the example project, add the NAND Flash Controller IP to the block design by clicking on the + sign (Ctrl +I) and make the necessary connections as shown in below Figure

Figure 8: Adding the NAND Flash Controller IP to the block design

- 2. Upgrade the IP by clicking on Reports→Report IP Status present on the toolbar of the Vivado tool if required

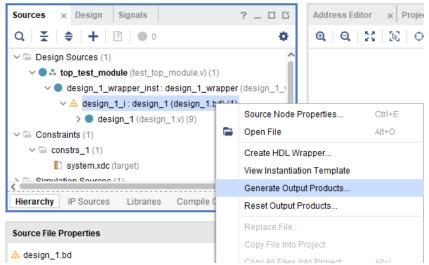

- 3. Save the Block design, validate it (Press F6) and generate the block design by right clicking on the design\_1(block design)→generate output products in the sources tab of the Vivado tool

Figure 9: Generate output products

4. After generating output products, right click on the design\_1→Create HDL wrapper and click on the 2<sup>nd</sup> option as shown in below Figure and click ok

#### **NAND Flash Controller Integration Manual**

Figure 10: Create HDL wrapper

5. Make Signal connections between the design\_1\_wrapper that contains NAND flash signals and the top\_test\_module in the top\_test\_module. v of the example design as shown in below Figure

```

// IP Integrator block Instantiation

design_1_wrapper design_1_wrapper_inst

(.DDR_addr

(DDR addr)

.DDR ba

(DDR_ba),

.DDR_cas_n

(DDR_cas_n),

(DDR_ck_n),

.DDR_ck_n

.DDR ck p

(DDR_ck_p),

.DDR cke

(DDR cke),

.DDR_cs_n

(DDR_cs_n),

.DDR dm

(DDR dm),

.DDR_dq

(DDR_dq),

.DDR_dqs_n

(DDR_dqs_n),

(DDR_dqs_p),

.DDR_dqs_p

.DDR odt

(DDR odt),

.DDR_ras_n

(DDR_ras_n),

.DDR_reset_n

(DDR_reset_n),

.DDR_we_n

(DDR_we_n),

.DDR_VRN

(DDR_VRN),

.DDR_VRP

(DDR_VRP),

.MIO

(MIO),

.PS_CLK

(PS_CLK)

.PS PORB

(PS PORB),

.PS SRSTB

(PS SRSTB),

.GPIO tri o

(gpio_tri_io),

.GPIO_1_tri_o

(gpio_1_tri_io),

(gpio_2_tri_io),

.GPIO_2_tri_o

.GPIO2_tri_o

(gpio2_tri_io),

// NAND Flash Interface

.nand_r_b_n_i ( nand_r_b_n

.nand_ce_0_n_o

( nand_ce_0_n_o

, mand_ce_0_n_o

( nand_ce_1_n_o

( nand_ce_1_n_o)

.nand_ce_1_n_o

.nand_re_n_o

.nand_we_n_o

( nand re n o

( nand_we_n_o

.nand_cle_o

( nand cle o

.nand ale o

( nand ale o

( nand_wp_n_o

( nand_data_io

.nand_wp_n_o

.nand_data_io

.nand_data_dir_o

( nand data dir o

```

Figure 11: Instantiation of NAND Host IP in NAND Flash Controller module

- 6. Give the pin constraint for NAND interface using .xdc file as shown in below figure

- 7. Save the project and Generate the Bit stream file

## 3 Implementation Details

#### 3.1 Parameter Settings

NAND IP consists of several parameters. These are to be set before compiling the project. The values of the parameters can be found from the NAND Datasheet. Following are the parameters required by the NAND Host Controller.

TPWR : Power-On Recovery Time

TRST : Device Resetting Time

TR\_ECC : Data Transfer Time Flash Array to Data Register, Internal ECC Enabled

TR : Data Transfer Time Flash Array to Data Register, Internal ECC Disabled

5. TPROG : PROGRAM PAGE Operation Time6. TBERS : BLOCK ERASE Operation Time

7. TWB :WE# HIGH to Busy

8. TFEAT :Busy Time for FEATURES command operations

9. TWHR :WE# HIGH to RE# LOW 10. TCCS :Column Address Set Time

11. DEV\_PG\_SIZE :Page size of the NAND device

12. DEV\_OOB\_SIZE:OOB size of the NAND device

Most of the parameters are given as the maximum time; these have to be considered as it is. Parameters given with minimum time, additionally consider a buffer time of 50-100ns. Get the values of the timing parameters (ns or us) from the datasheet and using the following example apply all the values to the above parameters. Consider the TRST time, in datasheet this time is defined as 500us (MAX). Based on the clock configured say, it is 100MHz (10ns). Then set the TRST parameter with value = 500us/10ns = 50000d If clock configured is 50MHz(20ns), set the TRST as 500us/20ns = 25000d, Similarly other parameters are to be added before compilation, in the file top\_test\_module.v.

NOTE: All the above parameters calculations is done with respect to the frequency of 100MHz and values shown is for Micron MT29F64G08AFAAA part. This is just for reference.

#### 3.2 Constraints

Following figure shows the example pin and IO standard constraints.

```

set_property PACKAGE_PIN C20 [get_ports nand_r_b_0_n_i]

set property PACKAGE PIN B19 [get ports nand r b l n i]

set property PACKAGE_PIN J20 [get ports nand_ce_0_n_o]

set property PACKAGE_PIN M17 [get ports nand_ce_1_n_o]

set property PACKAGE_PIN L19 [get_ports nand_re_n_o]

set property PACKAGE_PIN D19 [get ports nand_we_n_o]

set property PACKAGE_PIN F19 [get_ports nand_cle_o]

set property PACKAGE PIN K14 [get ports nand ale_o]

set_property PACKAGE_PIN E17 [get_ports nand_wp_n_o]

set property PACKAGE_PIN N15 [get_ports nand_data_dir_o]

set property PACKAGE_PIN G19 [get ports {nand_data_io[0]}]

set property PACKAGE_PIN L14 [get_ports {nand_data_io[1]}]

set property PACKAGE_PIN N20 [get ports {nand_data_io[2]}]

set property PACKAGE_PIN V17 [get ports {nand_data_io[3]}]

set property PACKAGE_PIN T16 [get ports {nand data_io[4]}]

set property PACKAGE_PIN N17 [get ports {nand_data_io[5]}]

set property PACKAGE PIN T20 [get ports {nand data io[6]}]

set property PACKAGE_PIN W18 [get ports {nand_data_io[7]}]

set property IOSTANDARD LVCMOS33 [get ports nand_r_b_0_n_i]

set property IOSTANDARD LVCMOS33 [get ports nand_r_b_1_n_i]

set property IOSTANDARD LVCMOS33 [get ports nand ce 0 n o]

set property IOSTANDARD LVCMOS33 [get ports nand_ce_1_n_o]

set property IOSTANDARD LVCMOS33 [get ports nand_re_n_o]

set property IOSTANDARD LVCMOS33 [get ports nand_we_n_o]

set property IOSTANDARD LVCMOS33 [get ports nand_cle_o]

set property IOSTANDARD LVCMOS33 [get ports nand_ale_o]

set property IOSTANDARD LVCMOS33 [get_ports nand_wp_n_o]

set property IOSTANDARD LVCMOS33 [get ports nand_data_dir_o]

set property IOSTANDARD LVCMOS33 [get_ports {nand_data_io[0]}]

set property IOSTANDARD LVCMOS33 [get ports {nand_data_io[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {nand_data_io[2]}]

set property IOSTANDARD LVCMOS33 [get ports {nand data io[3]}]

set property IOSTANDARD LVCMOS33 [get ports {nand_data_io[4]}]

set property IOSTANDARD LVCMOS33 [get ports {nand_data_io[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {nand_data_io[6]}]

set property IOSTANDARD LVCMOS33 [get ports {nand_data_io[7]}]

```

Figure 12: Pin Constraints in example design .xdc file

#### NOTE:

These constraints are in accordance to example design for XC7Z020CLG400-1 FPGA device. Please change the pin constraints for NAND interface for other custom board. Also define the constraints for clock, reset and UART pins accordingly if required for custom board.

GPIO Pins can be used in .xdc file if required.

# 4 FPGA Implementation

#### **4.1 Resource Utilization**

The table below shows the utilization summary from the implementation of NAND Flash Host Controller for Zynq-7000 SoC FPGA device with part number XC7Z020CLG400-1.

Table 2: Device Utilization Summary for NAND Flash Host Controller IP

| Resource<br>LUT | Utilization 2137 | Available 53200 |

|-----------------|------------------|-----------------|

| FF              | 1242             | 106400          |

| BRAM            | 8                | 140             |